## **Brief Description**

The ZAMC4100 Actuator and Motor Controller is an integrated, single package solution that features a high-performance ARM<sup>®</sup> Cortex<sup>™</sup>-M0\* microcontroller (MCU), a 10-bit ADC, four general purpose analog inputs, four half-bridge drivers, four high-side switches, one output buffer for electrochromatic (EC) mirror control with programmable output voltage (6 bit DAC), current source for external diode-based temperature measurements, switchable voltage source for external resistive sensors, and LIN (Local Interconnect Network) bus interface.

This single-package solution with its rich diagnostic features, optimized thermal performance, and LIN bus interface, is well suited for automotive applications, such as high-end automotive exterior mirror controllers, where small form-factor circuit board designs and light wiring harnesses are required.

## Features

- Two main operation modes

- NORMAL Mode with all functionality available

- SLEEP Mode with very low current consumption (less than 80µA)

- 10-bit ADC for measuring various parameters

- 4 general purpose ADC inputs configurable for absolute or ratiometric mode

- 4 low RDS (ON) half-bridge drivers and 4 low RDS (ON) high-side switches

- Analog EC mirror output controlled via 6-bit DAC

- All outputs short circuit protected

- Hardware 8-bit PWM control for half-bridge and high-side drivers

- Over-temperature protection with automatic driver shut-down

- Over-voltage and under-voltage detection with automatic driver shut-down

- Overload and open/short diagnostic for all outputs

- Embedded LIN 2.2/SAE J2602-2 transceiver

- Embedded ARM<sup>®</sup> Cortex<sup>™</sup>-M0 microcontroller

- 8 user-configurable GPIO pins

## Benefits

- Multi-chip-module concept with high functional integrity

- · Low number of external components

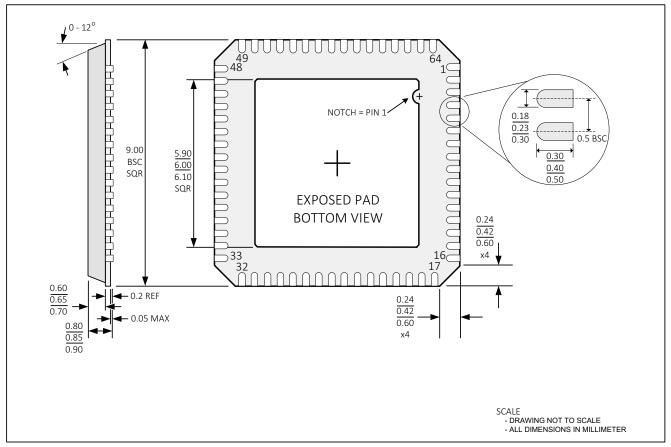

- Small footprint plastic QFN package with exposed pad allowing better thermal management

- AEC-Q100 qualified product, optimized for automotive environment

- Smart power management concept for achieving low sleep current consumption (<80µA)

## **Available Support**

- Data sheet and application notes

- Evaluation and Application Kits

- Software Development Kit (SDK)

## **Physical Characteristics**

- Ambient operation temperature: -40°C to +85°C

- Wide power supply voltage range: 6V to 18V

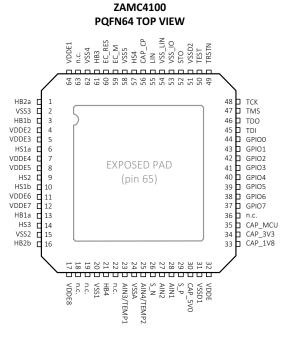

- Plastic QFN64 9x9mm package; exposed die pad

\* Note: The ARM® and Cortex™ trademarks are owned by ARM, Ltd.

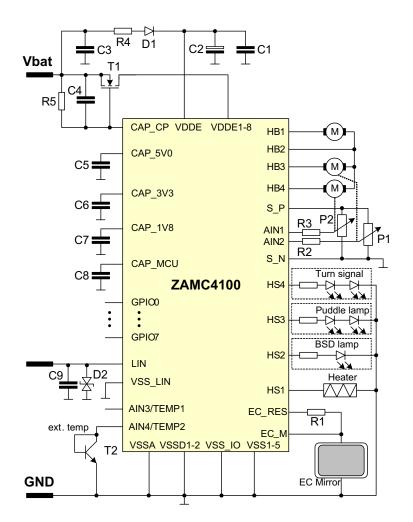

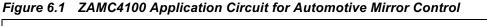

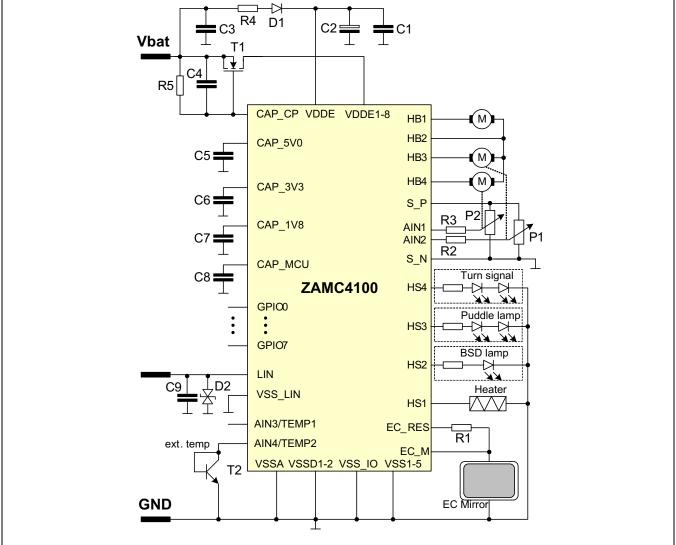

## ZAMC4100 Application Circuit for Automotive Mirror Control

## Typical Applications

- Automotive exterior rear view

mirror controllers

- Intelligent DC motor drivers

- Stand alone or slave actuator controllers

- Power management for low voltage electrical systems

- Single chip solution for optimized white goods' controllers

Note: Refer to the *ZAMC4100 Data Sheet* for the values and functions of the external components in the application circuit.

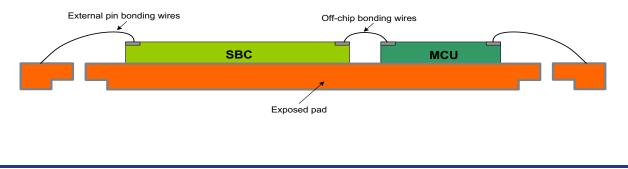

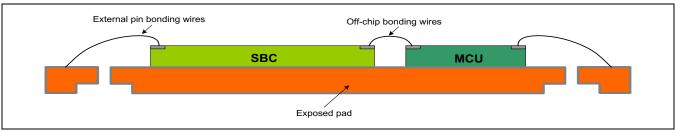

## Multi-Chip-Module Assembly: Microcontroller Unit (MCU) and System Basis Chip (SBC)

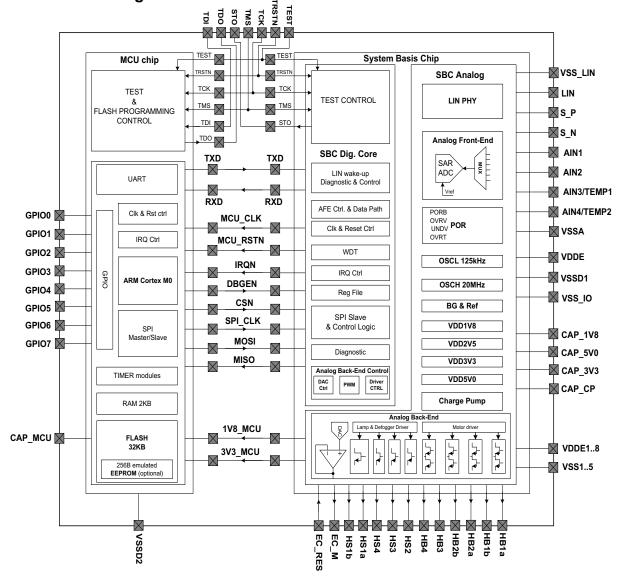

## ZAMC4100 Block Diagram

| SENSORS INTERFACE PINS | DESCRIPTION                                        |

|------------------------|----------------------------------------------------|

| S_P                    | Positive supply for sensors (5V)                   |

| S_N                    | Negative supply for sensors (0V)                   |

| AIN1                   | General purpose ADC input                          |

| AIN2                   | General purpose ADC input                          |

| AIN3/TEMP1             | General purpose ADC input/temperature sensor input |

| AIN4/TEMP2             | General purpose ADC input/temperature sensor input |

| ACTUATORS    | DESCRIPTION                                                         |

|--------------|---------------------------------------------------------------------|

| HB1a         | Output of holf bridge driver 1                                      |

| HB1b         | Output of half-bridge driver 1                                      |

| HB2a         | Output of half-bridge driver 2                                      |

| HB2b         | Output of half-bridge driver 2                                      |

| HB3          | Output of half-bridge driver 3                                      |

| HB4          | Output of half-bridge driver 4                                      |

| HS1a         | Output of high side output 1                                        |

| HS1b         | Output of high-side switch 1                                        |

| HS2          | Output of high-side switch 2                                        |

| HS3          | Output of high-side switch 3                                        |

| HS4          | Output of high-side switch 4                                        |

| EC_M         | Output for EC mirror control                                        |

| EC_RES       | Connection to external resistor for EC                              |

| SERVICE PINS | DESCRIPTION                                                         |

| CAP_5V0      | Connection to external capacitor for 5V (SBC analog core supply)    |

| CAP_3V3      | Connection to external capacitor for 3.3V (MCU peripheral supply)   |

| CAP_1V8      | Connection to external capacitor for 1.8V (SBC digital core supply) |

| CAP_MCU      | Connection to external capacitor for 1.8V<br>(MCU core supply)      |

| CAP_CP       | Connection to external capacitor for CP                             |

| EXPOSED PAD  | Connected to digital ground                                         |

| COMMUNICATION<br>INTERFACE PINS | DESCRIPTION                          |

|---------------------------------|--------------------------------------|

| LIN                             | LIN bus                              |

| GPIO0 to GPIO7                  | General purpose I/O pins             |

| TEST INTERFACE<br>PINS          | DESCRIPTION                          |

| TEST                            | Global test enable pin               |

| TRSTN                           | JTAG Low-active Reset                |

| ТСК                             | JTAG clock                           |

| TMS                             | JTAG Mode Select                     |

| TDO                             | JTAG data out pin                    |

| TDI                             | JTAG data in pin                     |

| STO                             | SBC test data out                    |

| SUPPLY PINS                     | DESCRIPTION                          |

| VDDE                            | Supply for the system                |

| VDDE1 to VDDE8                  | High current supply for the drivers  |

| VSS1 to VSS5                    | High current ground for drivers      |

| VSS_LIN                         | Ground for LIN transceiver           |

| VSSA                            | Ground for analog blocks (low noise) |

| VSSD1                           | Ground for digital blocks of SBC     |

| VSSD2                           | Ground for MCU                       |

|                                 | Ground for SBC digital IOs           |

#### **Ordering Information**

| Product Sales Code                                                                                               | Description                                           | Package           |

|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------|

| ZAMC4100GA2R                                                                                                     | ZAMC4100GA PQFN64 – Temperature range: -40°C to +85°C | 13" Tape and Reel |

| ZAMC4100GA2V                                                                                                     | ZAMC4100GA PQFN64 – Temperature range: -40°C to +85°C | Tray              |

| ZAMC4100 Evaluation Kit V2.0 including the ZAMC4100 Evaluation Board; software available at www.IDT.com/ZAMC4100 |                                                       |                   |

| ZAMC4100 Application Kit V1.0 including the ZAMC4100 Application Board                                           |                                                       |                   |

Corporate Headquarters 6024 Silver Creek Valley Road San Jose, CA 95138 www.IDT.com Sales 1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com/go/sales

## Tech Support

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) reserves the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of any kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit <u>www.idt.com/go/glossary</u>. All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved.

## Contents

| 1 | IC C | Characteristics                                   | 14 |

|---|------|---------------------------------------------------|----|

|   | 1.1. | Absolute Maximum Ratings                          | 14 |

|   | 1.2. | Electrical Parameters                             | 15 |

|   | 1.2. | 1. Supply and Supply Monitoring                   | 15 |

|   | 1.2. | 2. Digital Interface (GPIOs)                      | 17 |

|   | 1.2. | 3. LIN Physical Layer                             | 17 |

|   | 1.2. | 4. Output Drivers                                 | 18 |

|   | 1.2. | 5. Internal Reference Sources and Sensors         | 21 |

|   | 1.2. | 6. Analog-to-Digital Converter                    | 22 |

|   | 1.3. | Timing Parameters                                 | 22 |

|   | 1.3. | 1. Oscillators (OSCL and OSCH)                    | 22 |

|   | 1.3. | 2. Analog-to-Digital Converter                    | 23 |

|   | 1.3. | 3. SPI Bus Timing                                 | 24 |

|   | 1.3. | 4. System Power-up Timing                         | 25 |

|   | 1.4. | MCU Flash Memory Parameters                       | 26 |

| 2 | Sys  | tem Blocks Description                            | 27 |

|   | 2.1. | Power Supply                                      | 27 |

|   | 2.2. | High-Frequency and Low-Frequency Oscillator       | 28 |

|   | 2.3. | Watchdog Timer                                    | 28 |

|   | 2.4. | Analog-to-Digital Converter                       |    |

|   | 2.5. | Output Drivers                                    |    |

|   | 2.6. | Driver's Power Capability and Package Temperature |    |

|   | 2.7. | LIN Interface                                     | 30 |

|   | 2.8. | SPI Bus                                           |    |

|   | 2.9. | Diagnostic Functionalities                        |    |

|   |      | Microcontroller ARM® Cortex™ M0                   |    |

|   |      | 0.1. MCU GPIOs                                    |    |

|   |      | 0.2. MCU Timer Module                             |    |

|   |      | 0.3. MCU SPI Master                               |    |

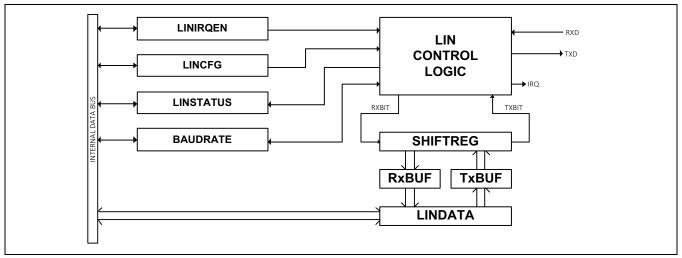

|   |      | 0.4. MCU LIN Controller                           |    |

| 3 | ZAN  | MC4100 SBC Functional Description                 |    |

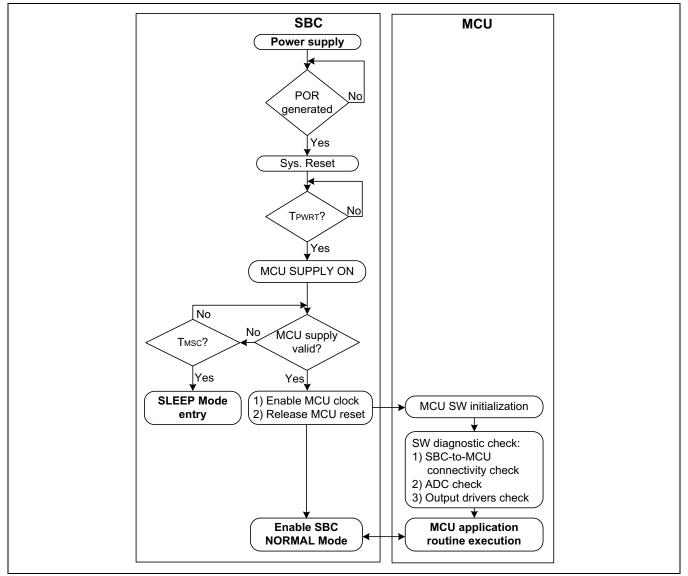

|   | 3.1. | System Power-Up Sequence                          |    |

|   | 3.2. | Clock and Reset Sources of the ZAMC4100           |    |

|   | 3.2. |                                                   |    |

|   | 3.2. |                                                   |    |

|   |      | Watchdog Timer (WDT)                              |    |

|   | 3.3. | 1. WDT Structure and Operation Principals         | 38 |

# () IDT.

| 3.3.2.   | WDT during SLEEP and STANDBY Mode                                                 | 40 |

|----------|-----------------------------------------------------------------------------------|----|

| 3.3.3.   | WDT Configuration Register                                                        | 40 |

| 3.4. Sy  | stem Supply Monitoring                                                            | 41 |

| 3.4.1.   | Over-Voltage and Under-Voltage Detection                                          | 41 |

| 3.4.2.   | ZAMC4100 Operation during Over-Voltage                                            | 42 |

| 3.4.3.   | ZAMC4100 Operation during Under-Voltage                                           | 42 |

| 3.4.4.   | Charge Pump Voltage Monitoring                                                    | 42 |

| 3.5. ZA  | MC4100 System Operational Modes                                                   | 43 |

| 3.5.1.   | NORMAL Mode                                                                       | 43 |

| 3.5.2.   | SLEEP Mode                                                                        | 44 |

| 3.5.3.   | STANDBY Mode                                                                      | 46 |

| 3.5.4.   | Supported Wake-up Sources                                                         | 46 |

| 3.5.5.   | Operational Modes Control                                                         | 47 |

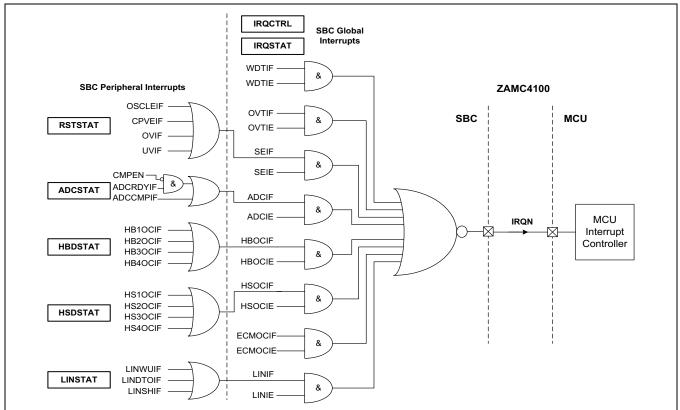

| 3.6. SE  | 3C Interrupts                                                                     | 49 |

| 3.6.1.   | SBC Interrupts: Enabling, Flagging, and Clearing Procedure                        | 50 |

| 3.6.2.   | SBC Global Interrupts Registers                                                   | 50 |

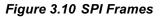

| 3.7. Se  | rial Peripheral Interface (SPI) Bus Interface                                     | 54 |

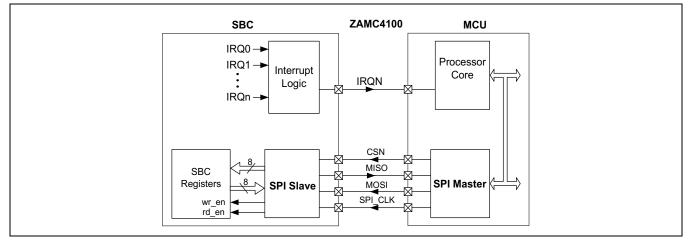

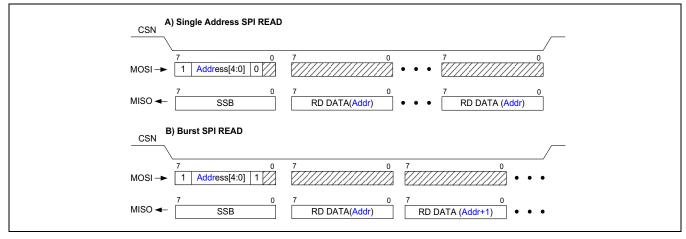

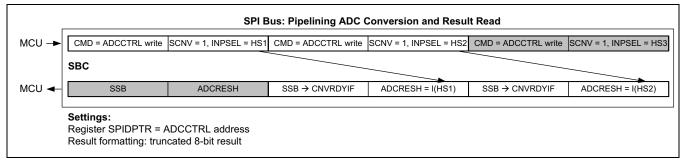

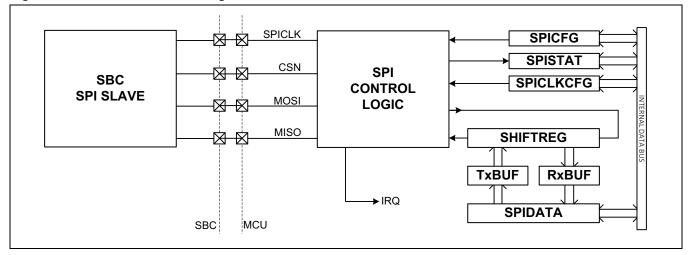

| 3.7.1.   | SBC and MCU SPI Connection Principles                                             | 55 |

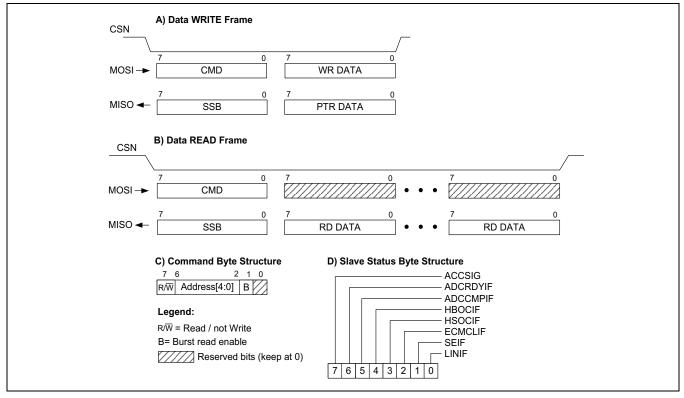

| 3.7.2.   | SPI Write Access                                                                  | 56 |

| 3.7.3.   | SPI Pipelined Write/Read Access                                                   | 57 |

| 3.7.4.   | SPI Read Access                                                                   | 57 |

| 3.7.5.   | SPI Slave Status Byte                                                             | 58 |

| 3.8. Ha  | alf-Bridge Drivers                                                                | 59 |

| 3.8.1.   | Half-Bridge Drivers Control and Status Register                                   | 60 |

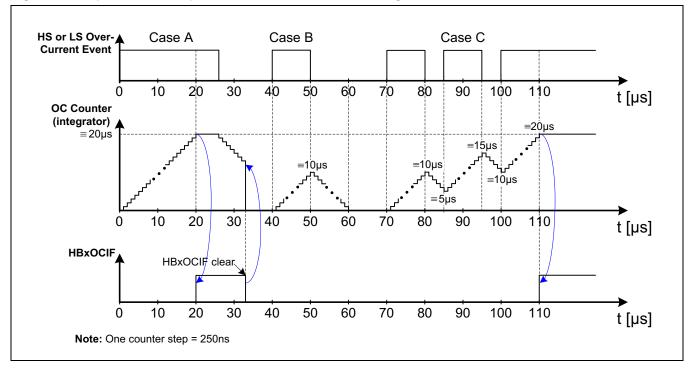

| 3.8.2.   | Half-Bridge Over-Current Protection                                               | 61 |

| 3.8.3.   | Half-Bridge Driver Output Diagnostic Check                                        | 63 |

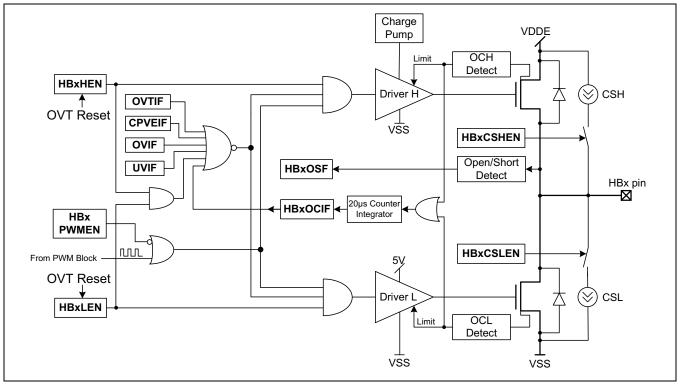

| 3.9. Hi  | gh-Side Drivers                                                                   | 65 |

| 3.9.1.   | High-Side Control and Status Register                                             | 66 |

| 3.9.2.   | High-Side Over-Current Protection                                                 | 66 |

| 3.9.3.   | High-Side Drivers Output Diagnostic Check                                         | 66 |

| 3.10. Pu | Ilse Width Modulation (PWM)                                                       | 68 |

| 3.10.1.  | Overview                                                                          | 68 |

| 3.10.2.  | PWM Signal Generation                                                             | 69 |

| 3.10.3.  | Drivers PWM Control                                                               | 70 |

| 3.10.4.  | PWM Initialization                                                                | 71 |

| 3.10.5.  | PWM Module in SLEEP and STANDBY Mode                                              | 72 |

| 3.11. EC | C Mirror Driver                                                                   | 72 |

| 3.11.1.  | ECM Driver Current/Voltage Limitation and Protection against Short to GND or Vbat | 73 |

|          |                                                                                   |    |

© 2016 Integrated Device Technology, Inc.

| 3.11.2.   | ECM Control Register                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75                                         |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|

| 3.11.3.   | ECM Driver Output Diagnostic Check                                                                                                                                                                                                                                                                                                                                                                                                                                             | 76                                         |

| 3.12. ZA  | MC4100 Analog to Digital Converter                                                                                                                                                                                                                                                                                                                                                                                                                                             | 77                                         |

| 3.12.1.   | ADC Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 77                                         |

| 3.12.2.   | ADC External Inputs Configuration                                                                                                                                                                                                                                                                                                                                                                                                                                              | 79                                         |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

| 3.12.4.   | ADC Voltage References and Result Calculation                                                                                                                                                                                                                                                                                                                                                                                                                                  | 84                                         |

| 3.12.5.   | ADC Configuration and ADC Status Register                                                                                                                                                                                                                                                                                                                                                                                                                                      | 85                                         |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

| 3.12.7.   | ADC Single and Continuous Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                           | 88                                         |

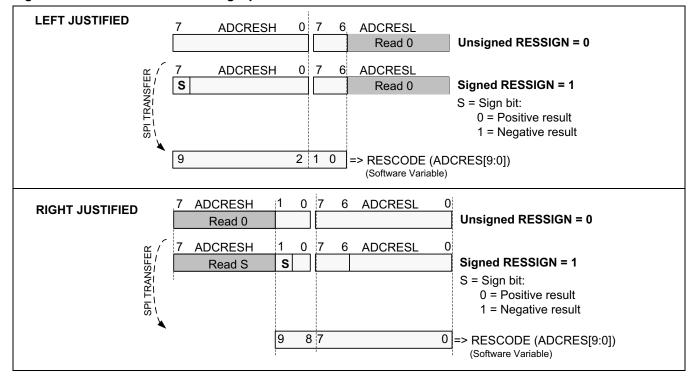

| 3.12.8.   | ADC Result Formatting Options                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 89                                         |

| 3.12.9.   | ADC Comparator and Counter                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 91                                         |

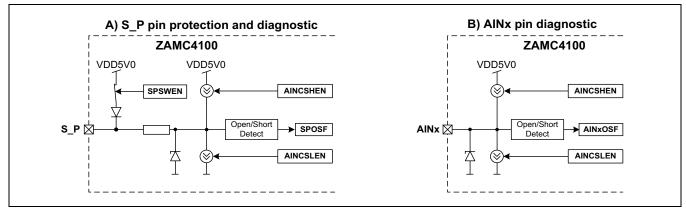

| 3.12.10   | External ADC Analog Inputs Open/Short Diagnostics and Protection                                                                                                                                                                                                                                                                                                                                                                                                               | 92                                         |

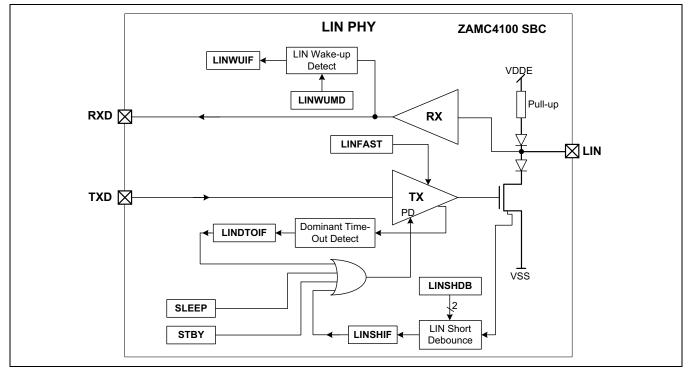

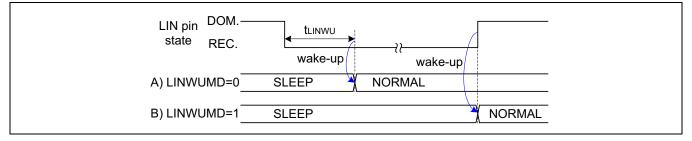

| 3.13. LIN | I Physical Layer (LIN PHY)                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 95                                         |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

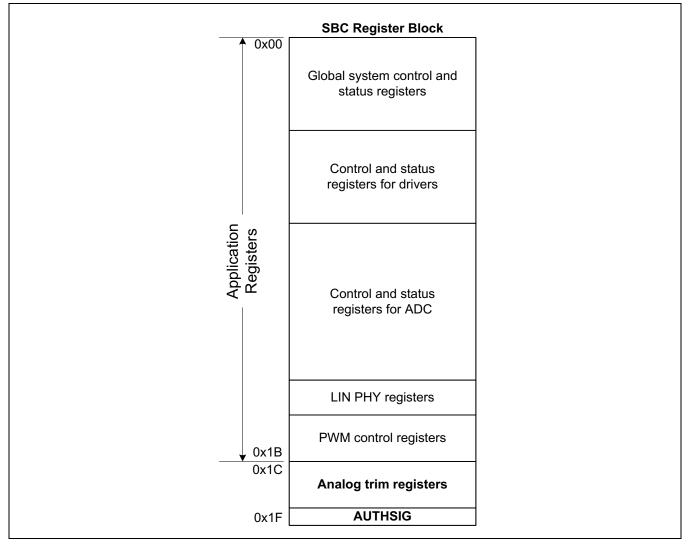

| 3.14.1.   | SBC Registers Address Map                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 100                                        |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                            |

|           | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

| 4.2. Me   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

| 4.2.1.    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           | ,                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                            |

|           | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                            |

| 4.6. 32-  | Bit TIMER Module                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 112                                        |

|           | 3.11.3.<br>3.12. ZA<br>3.12.1.<br>3.12.2.<br>3.12.3.<br>3.12.4.<br>3.12.5.<br>3.12.6.<br>3.12.6.<br>3.12.7.<br>3.12.8.<br>3.12.9.<br>3.12.10<br>3.13. LIN<br>3.13.1.<br>3.13.2.<br>3.14. SB<br>3.14.1.<br>3.13.2.<br>3.14. SB<br>3.14.1.<br>3.14.2.<br>3.14.2.<br>3.14.2.<br>3.14.2.<br>3.14.2.<br>3.14.2.<br>3.14.2.<br>4.2.1.<br>4.2.2.<br>4.2.3.<br>4.2.4.<br>4.2.4.<br>4.3. MC<br>4.4. MC<br>4.4.1.<br>4.4.2.<br>4.5. GP<br>4.5.1.<br>4.5.2.<br>4.5.3.<br>4.5.4.<br>4.5.6. | 3.11.3. ECM Driver Output Diagnostic Check |

© 2016 Integrated Device Technology, Inc.

|   | 4.6.1.  | Timer Mode (MODETC = 0)                                                                      | . 113 |

|---|---------|----------------------------------------------------------------------------------------------|-------|

|   | 4.6.2.  | Counter Mode (MODETC = 1)                                                                    | . 113 |

|   | 4.6.3.  | TIMER Module Interrupt                                                                       | . 113 |

|   | 4.6.4.  | TIMER Module Registers                                                                       | . 113 |

| 4 | .7. Sys | Tick                                                                                         | . 113 |

| 4 | .8. Ma  | ster SPI Module                                                                              | . 114 |

|   | 4.8.1.  | Overview                                                                                     |       |

|   | 4.8.2.  | Setup Requirements for the Slave SPI of SBC                                                  | . 114 |

|   | 4.8.3.  | SPI Data Transfer Process                                                                    | . 115 |

|   | 4.8.4.  | Continuous SPI Data Streaming                                                                | . 115 |

|   | 4.8.5.  | Abrupt SPI Discontinuity                                                                     | . 115 |

|   | 4.8.6.  | Interrupts and Status Flags in the Z1_SPISTAT Register                                       | . 115 |

|   | 4.8.7.  | Syncing the Data Transfer Rate via a Software Pause                                          | . 116 |

|   | 4.8.8.  | Master SPI Registers                                                                         | . 116 |

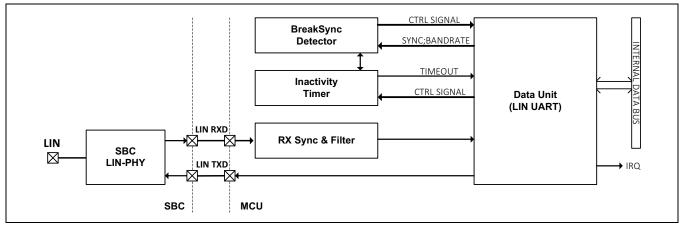

| 4 | .9. SW  | -LIN Module                                                                                  | . 117 |

|   | 4.9.1.  | The Inactivity Timer                                                                         |       |

|   | 4.9.2.  | The BREAK/SYNC Field Detector                                                                | . 118 |

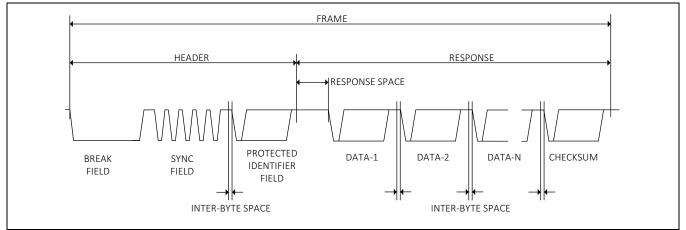

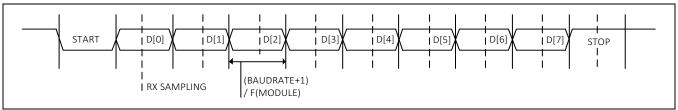

|   | 4.9.3.  | SW-LIN Data Unit                                                                             |       |

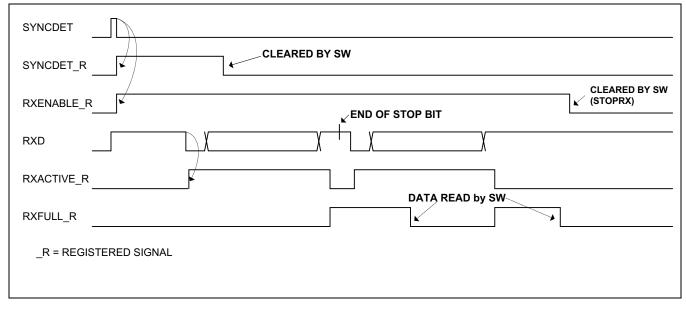

|   | 4.9.4.  | Description of the Receive Operation                                                         | . 119 |

|   | 4.9.5.  | Description of Transmit Operation                                                            | . 120 |

|   | 4.9.6.  | General Remarks for SW-LIN Usage                                                             | . 122 |

|   | 4.9.7.  | SW-LIN Registers                                                                             | . 122 |

| 4 | .10. MC | U Registers Description                                                                      | . 123 |

|   |         | System Registers                                                                             |       |

|   | 4.10.2. | GPIO Registers                                                                               | . 125 |

|   | 4.10.3. | 32 Bit Timer Registers                                                                       | . 128 |

|   |         | SPI Registers                                                                                |       |

|   | 4.10.5. | SW-LIN Registers                                                                             | . 132 |

|   | 4.10.6. | FLASH Memory Registers                                                                       | . 136 |

| 5 | ZAMC4   | 100 Protection and Diagnostic Features                                                       | . 140 |

| 5 |         | -Time Diagnostic and Protection Features                                                     |       |

|   |         | Over-Current (OC) Protection                                                                 |       |

|   | 5.1.2.  | Over-Load (OVL) Detection using the ADC                                                      | . 140 |

|   | 5.1.3.  | Over-Temperature (OVT) Protection                                                            |       |

|   | 5.1.4.  | Over-Voltage (OV) Detection                                                                  | . 141 |

|   | 5.1.5.  | Under-Voltage (UV) Detection                                                                 | . 141 |

|   | 5.1.6.  | Short to GND or Vbat Protection of Sensor Supply Pin S_P and Analog Input Pins AIN1 and AIN2 | . 141 |

|   | 5.1.7.  | OSCL Output Clock Failure Detection                                                          |       |

|   |         | •                                                                                            |       |

| 5  | 5.2. N | ICU Activated Diagnostic Functions                             | 142 |

|----|--------|----------------------------------------------------------------|-----|

|    | 5.2.1. | . Open-Load Detection                                          | 142 |

|    | 5.2.2. | . Short to Vbat or GND Detection                               | 142 |

|    | 5.2.3. | . Floating Analog Input Detection                              | 142 |

|    | 5.2.4. | . Short or Open Sensor Supply Detection                        | 143 |

|    | 5.2.5. | ADC Ratiometric Test                                           | 143 |

|    | 5.2.6. | ADC Test Absolute                                              | 143 |

|    | 5.2.7. | . Reference Voltage Test                                       | 144 |

|    | 5.2.8. |                                                                |     |

|    | 5.2.9. | . 2.5V Supply Test                                             | 144 |

|    | 5.2.10 | 0. Current Multiplexer Test                                    | 145 |

| 6  | Appli  | cation Circuit and External Components                         | 146 |

| 6  | 6.1. A | Application Circuit Diagram for Mirror Controller              | 146 |

| 6  | б.2. E | External Components for Automotive Mirror Control Application  | 147 |

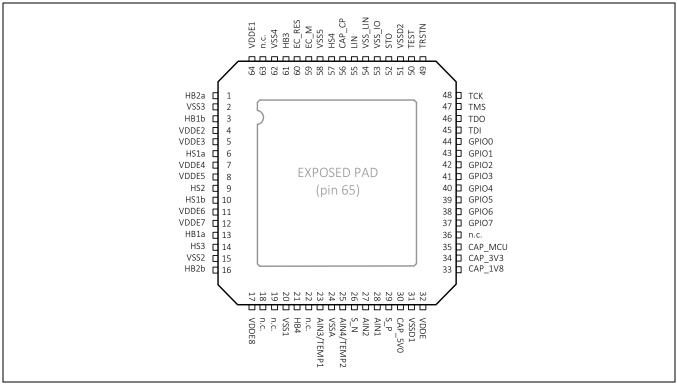

| 7  | Multi- | -chip Module Assembly, Pin Layout, and Pin Assignments         | 148 |

| 8  | ZAM    | C4100 Outline Dimensions: Plastic QFN64 9x9mm (Package Type 1) | 152 |

| 9  | Orde   | ring Information                                               | 153 |

| 10 |        | ed Documents                                                   |     |

| 11 |        | sary                                                           |     |

| 12 | Docu   | ment Revision History                                          | 155 |

|    |        |                                                                |     |

## List of Figures

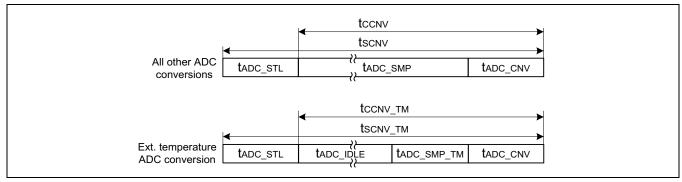

| Figure 1.1 | ADC Timing Parameters Definition                                              | 23 |

|------------|-------------------------------------------------------------------------------|----|

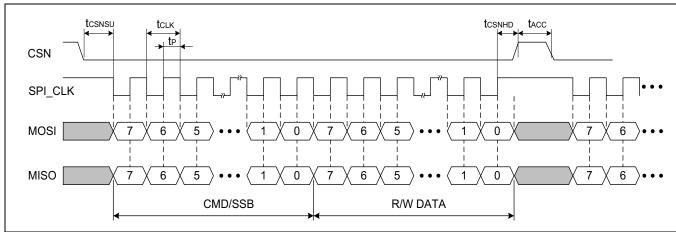

| Figure 1.2 | SPI Communication Timing Diagram                                              | 24 |

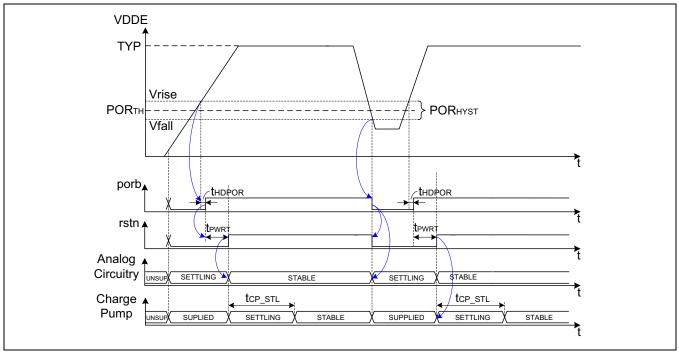

| Figure 1.3 | ZAMC4100 System Power-Up Sequence                                             | 25 |

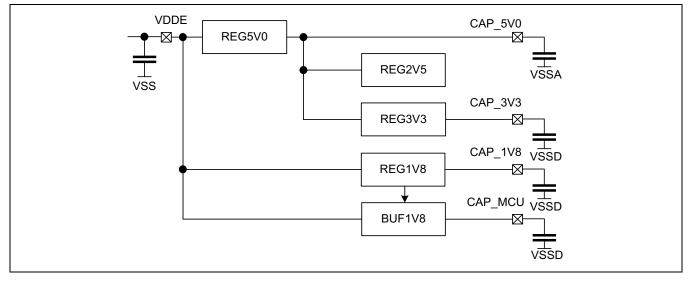

| Figure 2.1 | ZAMC4100 Supply Structure                                                     | 27 |

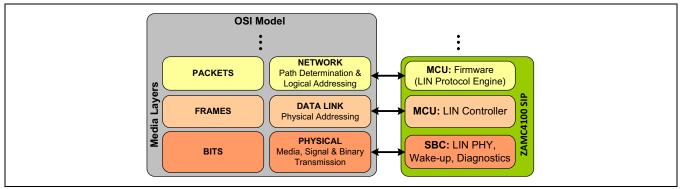

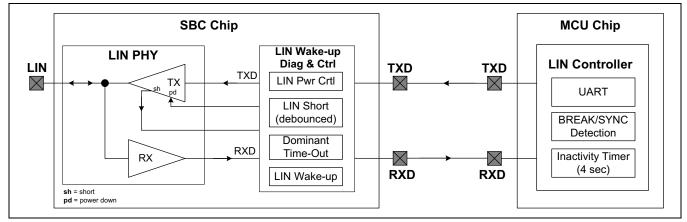

| Figure 2.2 | ZAMC4100 LIN Interface and Open Systems Interconnection (OSI) Layers Coverage | 30 |

| Figure 2.3 | LIN Slave Node Implementation in the ZAMC4100                                 | 30 |

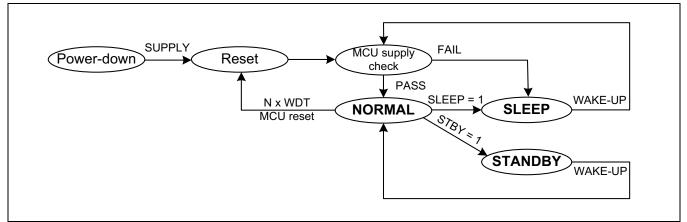

| Figure 3.1 | SBC Power-Up State Diagram                                                    | 33 |

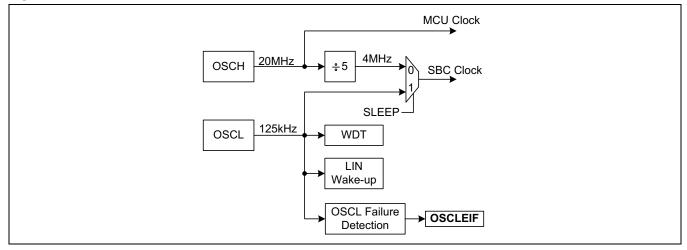

| Figure 3.2 | ZAMC4100 Clock Sources                                                        | 35 |

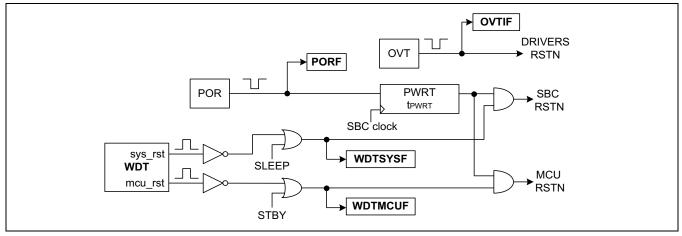

| Figure 3.3 | ZAMC4100 Reset Sources                                                        | 36 |

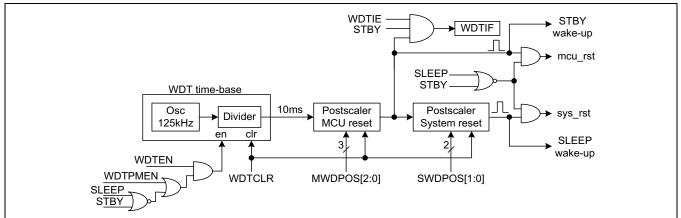

| Figure 3.4 | ZAMC4100 Watchdog Timer                                                       | 38 |

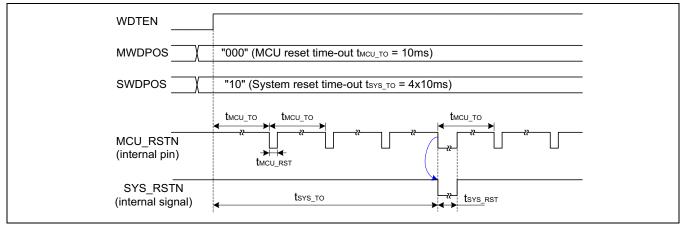

| Figure 3.5 | WDT Operation                                                                 | 39 |

| Figure 3.6 | ZAMC4100 Operational Modes                                                    | 43 |

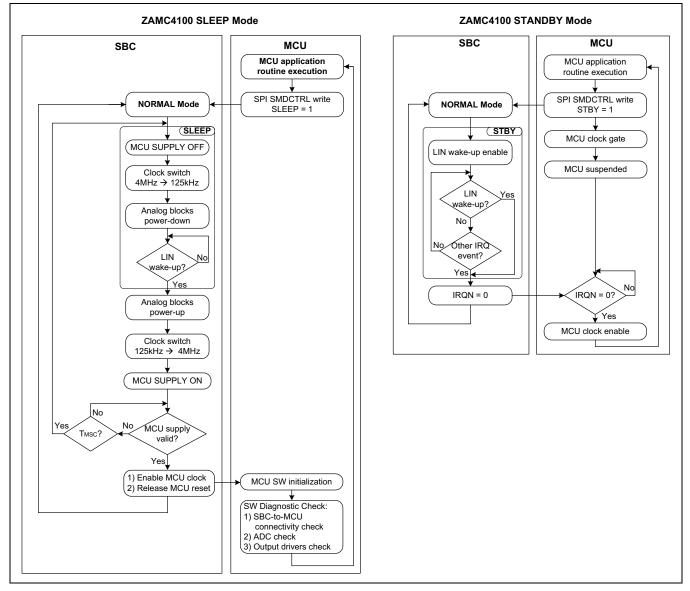

| Figure 3.7 | ZAMC4100 SLEEP and STANDBY Mode Behavior                                      | 45 |

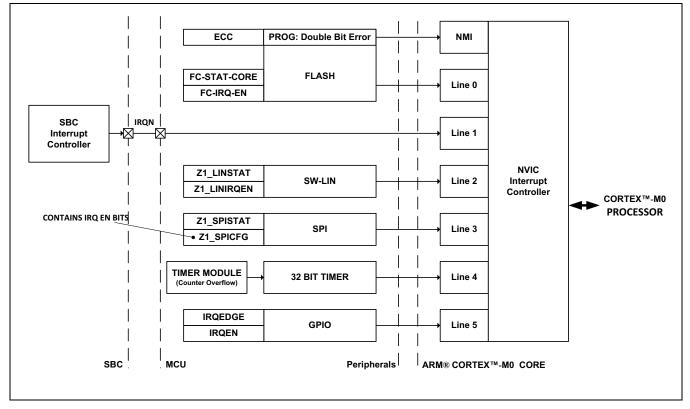

| Figure 3.8 | SBC Interrupt Logic Organization                                              | 49 |

| Figure 3.9 | MCU-to-SBC Connection via SPI                                                 |    |

@ 2016 Integrated Device Technology, Inc.

| SPI Frames                                                                  |                            |

|-----------------------------------------------------------------------------|----------------------------|

| SPI Single or Burst Access                                                  | 57                         |

| Structure of the Half-Bridge Drivers                                        | 59                         |

| Operation Principle of Over-Current Counter Integrator                      | 62                         |

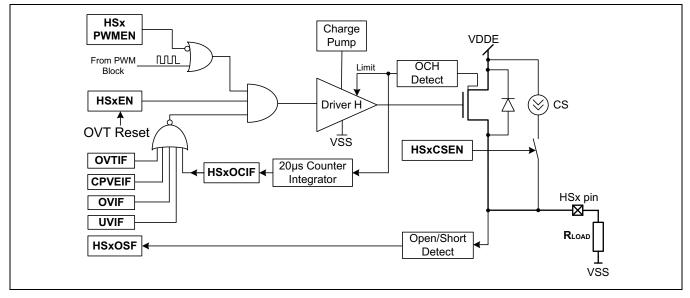

| Structure of High-Side Drivers                                              | 65                         |

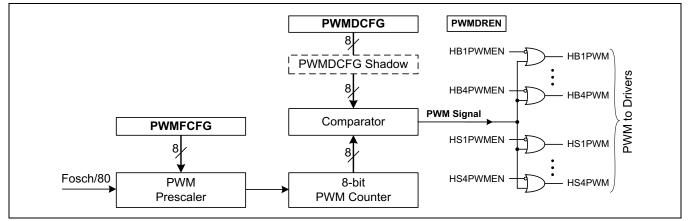

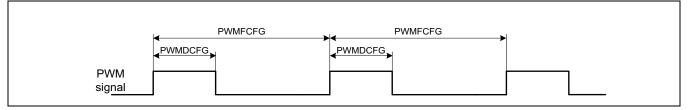

| PWM Block Diagram                                                           |                            |

|                                                                             |                            |

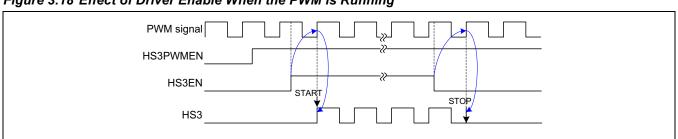

| Recommended PWM Initialization Procedure with HS3 as an Example             | 71                         |

| Effect of Driver Enable When the PWM is Running                             | 72                         |

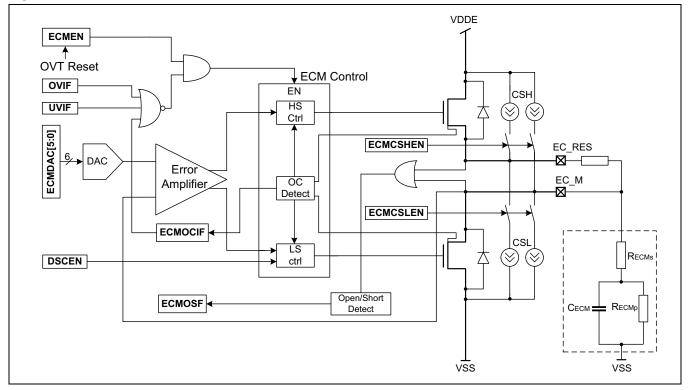

| ECM Driver Structure                                                        | 73                         |

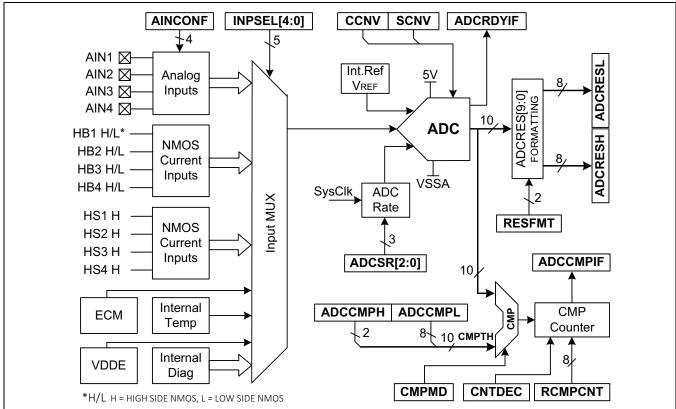

| ADC Functional Diagram                                                      |                            |

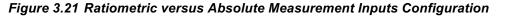

| Ratiometric versus Absolute Measurement Inputs Configuration                | 79                         |

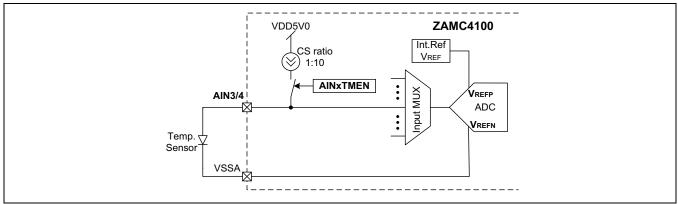

| Using AIN3 and AIN4 for External Temperature Measurement                    |                            |

|                                                                             |                            |

| ADC Result Formatting Options                                               |                            |

| ADC Analog Inputs Protection and Open/Short Detection Circuitry             |                            |

| LIN PHY Block Diagram                                                       |                            |

|                                                                             |                            |

| SBC Register File Organization                                              |                            |

| Structure of SBC Trimming Data                                              | 102                        |

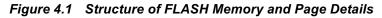

| Structure of FLASH Memory and Page Details                                  | 105                        |

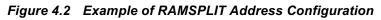

| Example of RAMSPLIT Address Configuration                                   |                            |

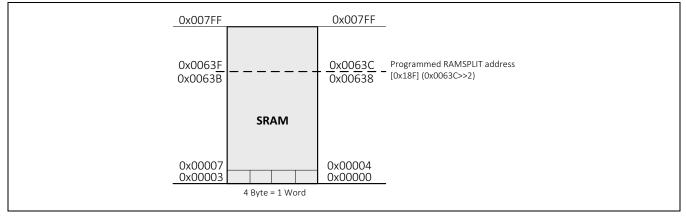

| RESET and CLOCK between SBC and MCU                                         | 109                        |

| MCU Interrupt Logic Organization                                            | 110                        |

| Master SPI Block Diagram                                                    |                            |

|                                                                             |                            |

|                                                                             |                            |

| Block Diagram of the LIN Data Unit                                          | 118                        |

| Frame Format of Each LIN Field (PID, DATA, Checksum) and RX Sample Position |                            |

| RX Control and Status Signal Waveforms                                      | 120                        |

| Waveforms of the TX and RX Control and Status Signals                       |                            |

| ZAMC4100 Application Circuit for Automotive Mirror Control                  | 146                        |

| ZAMC4100 Multi-chip-Module Assembly                                         |                            |

| Pin Layout for ZAMC4100 PQFN65 – Top View                                   |                            |

| ZAMC4100 Package Dimensions – Plastic QFN64                                 | 152                        |

|                                                                             | SPI Single or Burst Access |

## List of Tables

| Table 1.1  | Absolute Maximum Ratings                                              | 14 |

|------------|-----------------------------------------------------------------------|----|

| Table 1.2  | Thermal Specifications                                                | 14 |

| Table 1.3  | ESD Protection                                                        | 15 |

| Table 1.4  | Supply Voltages and Currents                                          | 15 |

| Table 1.5  | System Resets and Supply Monitoring                                   | 16 |

| Table 1.6  | GPIO Electrical Characteristics                                       | 17 |

| Table 1.7  | LIN Electrical Parameters                                             | 17 |

| Table 1.8  | Drivers Static Parameters                                             | 18 |

| Table 1.9  | EC Driver Static Parameters                                           | 19 |

| Table 1.10 | Drivers Dynamic Parameters                                            | 20 |

| Table 1.11 | Internal Die Temperature Sensor                                       | 21 |

| Table 1.12 | Internal Reference Sources                                            | 21 |

| Table 1.13 | ADC and Analog Input Pins Static Parameters                           | 22 |

| Table 1.14 | Timing Parameters: Low-Power Oscillator and High-Frequency Oscillator | 22 |

| Table 1.15 | ADC Timing Parameters                                                 | 23 |

| Table 1.16 | ZAMC4100 SPI Bus Timing Parameters                                    | 24 |

| Table 1.17 | System Power-up and Reset Timing Parameters                           |    |

| Table 1.18 | Flash Timing Parameters                                               | 26 |

| Table 3.1  | RSTSTAT Register Bits Mapping                                         | 37 |

| Table 3.2  | RSTSTAT Register Bits Description                                     | 37 |

| Table 3.3  | WDTCONF Register Bits Mapping                                         | 40 |

| Table 3.4  | WDTCONF Register Bits Description                                     | 41 |

| Table 3.5  | SMDCTRL Register Bits Mapping                                         | 47 |

| Table 3.6  | SMDCTRL Register Bits Description                                     | 48 |

| Table 3.7  | IRQCTRL Register Bits Mapping                                         | 51 |

| Table 3.8  | IRQCTRL Register Bits Description                                     | 52 |

| Table 3.9  | IRQSTAT Register Bits Mapping                                         | 53 |

| Table 3.10 | IRQSTAT Register Bits Description                                     | 53 |

| Table 3.11 | SPI Lines Description                                                 | 55 |

| Table 3.12 | SPI Slave Status Bits Descriptions (SSB)                              | 58 |

| Table 3.13 | HBDCTRL Register Bits Mapping                                         | 60 |

| Table 3.14 | HBDCTRL Bits Description                                              | 60 |

| Table 3.15 | HBDSTAT Register Bits Mapping                                         | 61 |

| Table 3.16 | HBDSTAT Register Bit Descriptions                                     | 61 |

| Table 3.17 | HBDDIAG Register Bits Mapping                                         |    |

| Table 3.18 | HBDDIAG Register Bits Description                                     | 63 |

| Table 3.19 | Half-Bridge Diagnostic Bit Descriptions                               | 64 |

| Table 3.20 | HSDCTRL Register Bits Mapping                   |      |

|------------|-------------------------------------------------|------|

| Table 3.21 | HSDCTRL Register Bits Description               | . 66 |

| Table 3.22 | HSDSTAT Register Bits Mapping                   | . 67 |

| Table 3.23 | HSDSTAT Register Bits Description               | . 67 |

| Table 3.24 | High-Side Diagnostic Bits Description           | . 67 |

| Table 3.25 | PWMDREN Register Bits Mapping                   | . 70 |

| Table 3.26 | PWMDREN Register Bits Description               |      |

| Table 3.27 | ECMCTRL Register Bits Mapping                   | . 75 |

| Table 3.28 | ECMCTRL Register Bits Description               | . 75 |

| Table 3.29 | ECMDIAG Register Bits Mapping                   | . 76 |

| Table 3.30 | ECMDIAG Register Bits Description               | . 76 |

| Table 3.31 | ECMOSF Diagnostic Bit Meaning                   | . 77 |

| Table 3.32 | AINCONF Register Bits Mapping                   | . 80 |

| Table 3.33 | AINCONF Register Bits Description               | . 81 |

| Table 3.34 | ADCCTRL Register Bits Mapping                   | . 82 |

| Table 3.35 | ADCCTRL Register Bits Description               | . 82 |

| Table 3.36 | Input MUX Control Bits Description              | . 83 |

| Table 3.37 | ADCCONF Register Bits Mapping                   | . 86 |

| Table 3.38 | ADCCONF Register Bits Description               |      |

| Table 3.39 | ADCSTAT Register Bits Mapping                   | . 87 |

| Table 3.40 | ADCSTAT Register Bits Description               | . 87 |

| Table 3.41 | ADC Sample-Rate Configuration                   | . 88 |

| Table 3.42 | ADCCMPH and ADCCMPL Bits Description            | . 91 |

| Table 3.43 | AINDIAG Register Bits Mapping                   | . 93 |

| Table 3.44 | AINDIAG Register Bits Description               | . 93 |

| Table 3.45 | External ADC Inputs Diagnostic Bits Description | . 94 |

| Table 3.46 | LINCTRL Registers Bit Mapping                   | . 97 |

| Table 3.47 | LINCTRL Registers Bits Description              | . 98 |

| Table 3.48 | LINSTAT Register Bits Mapping                   | . 98 |

| Table 3.49 | LINSTAT Register Bits Mapping                   | . 98 |

| Table 3.50 | SBC Registers Address Map                       | 100  |

| Table 4.1  | MCU Memory Map                                  | 104  |

| Table 4.2  | INFO Page 0 Structure                           | 107  |

| Table 4.3  | MCU Peripheral Interrupts                       | 111  |

| Table 4.4  | Configuration of Timer Trigger Behavior         | 113  |

| Table 4.5  | Register [0x4000_0000] SYS_CLKCFG               | 123  |

| Table 4.6  | Register [0x4000_0004] SYS_MEMPORTCFG           | 123  |

| Table 4.7  | Register [0x4000_0008] SYS_MEMINFO              | 124  |

|            |                                                 |      |

| Table 4.8  | Register [0x4000_000C] SYS_RSTSTAT                                                  | . 124 |

|------------|-------------------------------------------------------------------------------------|-------|

| Table 4.9  | Register [0x4000_1400] GPIO_DIR                                                     |       |

| Table 4.10 | Register [0x4000_1404] GPIO_IN                                                      | . 125 |

| Table 4.11 | Register [0x4000_1408] GPIO_OUT                                                     | . 126 |

| Table 4.12 | Register [0x4000_140C] GPIO_SETCLR                                                  | . 126 |

| Table 4.13 | Register [0x4000_1410] GPIO_IRQSTAT                                                 | . 126 |

| Table 4.14 | Register [0x4000_1414] GPIO_IRQEN                                                   | . 127 |

| Table 4.15 | Register [0x4000_1418] GPIO_IRQEDGE                                                 | . 127 |

| Table 4.16 | Register [0x4000_141C] GPIO_TRIGEN                                                  | . 127 |

| Table 4.17 | Register [0x4000_1000] T32_CTRL                                                     | . 128 |

| Table 4.18 | Register [0x4000_1004] T32_TRIGSEL                                                  | . 129 |

| Table 4.19 | Register [0x4000_1008] T32_CNT                                                      | . 129 |

| Table 4.20 | Register [0x4000_100C] T32_REL                                                      | . 129 |

| Table 4.21 | Register [0x4000_1820] Z1_SPICFG                                                    |       |

| Table 4.22 | Register [0x4000_1824] Z1_SPIDATA                                                   | . 130 |

| Table 4.23 | Register [0x4000_1828] Z1_SPICLKCFG                                                 | . 131 |

| Table 4.24 | Register [0x4000_182C] Z1_SPISTAT                                                   | . 131 |

| Table 4.25 |                                                                                     |       |

| Table 4.26 | 5 L _ J _                                                                           |       |

| Table 4.27 | Register [0x4000_1808] Z1_LINDATA                                                   | . 134 |

| Table 4.28 |                                                                                     |       |

| Table 4.29 | 5 1 _ 1 _                                                                           |       |

| Table 4.30 | ····                                                                                |       |

| Table 4.31 | Register [0x4000_0800] FC_RAM_ADDR                                                  |       |

| Table 4.32 | Register [0x4000_0804] FC_FLASH_ADDR                                                | . 136 |

| Table 4.33 |                                                                                     |       |

| Table 4.34 |                                                                                     |       |

| Table 4.35 |                                                                                     |       |

| Table 4.36 |                                                                                     |       |

| Table 4.37 | Register [0x4000_0818] FC_STAT_PROG                                                 |       |

| Table 4.38 | <b>o i</b> <u>-</u> <u>-</u> <u>-</u> <u>-</u>                                      |       |

| Table 6.1  | Parameters for External Components in Typical Automotive Mirror Control Application |       |

| Table 7.1  | Pin Description                                                                     | . 149 |

## **1** IC Characteristics

#### 1.1. Absolute Maximum Ratings

Stresses above those listed in this clause may cause immediate and permanent device failure. It is not implied that more than one of these conditions can be applied simultaneously. Operation outside the operating ranges for extended periods may affect device reliability. Total cumulative dwell time above the maximum operating rating for power supply or temperature must be less than 100 hours.

| Table 1.1 | Absolute | Maximum | Ratings |

|-----------|----------|---------|---------|

|-----------|----------|---------|---------|

| Parameter                                           | Symbol                | Value       | UNIT |

|-----------------------------------------------------|-----------------------|-------------|------|

| Supply Voltage                                      |                       |             |      |

| System supply voltage                               | V <sub>VDDE</sub>     | -0.3 to 28  | V    |

| System supply voltage under transient conditions    | V <sub>VDDE_max</sub> | -0.3 to 40  | V    |

| Input Pin Voltage                                   |                       |             |      |

| AIN1-4                                              | VIN(ANALOG)           | -0.3 to 5.5 | V    |

| GPIO0-7                                             | V <sub>IN(MCU)</sub>  | -0.3 to 3.6 | V    |

| LIN Bus Voltage                                     |                       |             |      |

| Bus voltage                                         | V <sub>BUS(SS)</sub>  | -18 to 40   | V    |

| Transient input voltage (per ISO7637 Specification) | V <sub>BUS(PK)</sub>  | -150 to 100 | V    |

| GPIO Supply current                                 | · · ·                 |             |      |

| Total GPIO sink/source current (referenced to 3.3V) | I <sub>GPIO</sub>     | 5           | mA   |

#### Table 1.2 Thermal Specifications

| Parameter                                               | Symbol           | Value      | UNIT |

|---------------------------------------------------------|------------------|------------|------|

| Thermal Ratings                                         |                  |            |      |

| Operating ambient temperature                           | T <sub>A</sub>   | -40 to 85  | °C   |

| Operating junction temperature <sup>1), 2)</sup>        | TJ               | -40 to 125 | °C   |

| Storage temperature                                     | T <sub>STG</sub> | -40 to 150 | °C   |

| Thermal Characteristics                                 | ····             |            |      |

| Thermal resistance junction to case <sup>3),4)</sup>    | Θ <sub>JC</sub>  | 0.4        | °C/W |

| Thermal resistance junction to ambient <sup>3),4)</sup> | Θ <sub>JA</sub>  | 21         | °C/W |

1) The limiting factor is the operating temperature of the FLASH memory within the MCU where the data retention is guaranteed for temperatures up to 85°C. In order to keep the MCU temperature below 85°C when the SBC is running at maximum temperature, the application should provide a sufficient heat sink. For more information, contact IDT technical support.

2) The device will automatically shut down the drivers at 125°C.

3) IDT uses test boards in conformance with the JESD51-7 (JEDEC) for thermal impedance measurement.

4) This value applies for the JEDEC board profile and specific environment only for package performance comparison. Care should be taken when applying in the actual application where the printed circuit board (PCB) profile and environment are different. Contact IDT technical support for assistance.

#### Table 1.3ESD Protection

| Test Method                                                                                                                                                                                                                                       | Test Setup Standard                            | Guaranteed ESD/Latch-up<br>Robustness on IC Level        |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------|----------------------------------------------------------|--|--|--|--|

| HBM (Human Body Model)                                                                                                                                                                                                                            | MIL 883C, Method 3015.7<br>or EIA/JESD22A114-A | $\pm$ 2kV (all pins) with 100pF and 1.5k $\Omega$        |  |  |  |  |

| CDM (Charged Device Model)                                                                                                                                                                                                                        | AEC – Q100 – 011 Rev. B                        | ± 500V (all pins)                                        |  |  |  |  |

| System Level (Human Body Discharge)                                                                                                                                                                                                               | IEC 61000-4-2                                  | $\pm$ 6kV for LIN <sup>(1)</sup> and VBAT <sup>(2)</sup> |  |  |  |  |

| Latch-up                                                                                                                                                                                                                                          | EIA/JESD78A                                    | 100mA@25°C                                               |  |  |  |  |

| <ul> <li>(1) External circuitry is required for meeting the system-level ESD specification for the LIN interface.</li> <li>(2) VBAT is the common supply terminal on the application PCB where all ZAMC4100 supply pins are connected.</li> </ul> |                                                |                                                          |  |  |  |  |

#### **1.2. Electrical Parameters**

Note: Parameters are specified for junction temperature range -40°C to 125°C unless otherwise stated.

#### 1.2.1. Supply and Supply Monitoring

#### Table 1.4 Supply Voltages and Currents

| Parameter                                                                       | Symbol               | Min. | Тур. | Max. | Unit |

|---------------------------------------------------------------------------------|----------------------|------|------|------|------|

| Supply Voltage Range (voltage drop in external circuitry not included)          | •                    |      |      |      |      |

| Nominal operating voltage                                                       | V <sub>SUP</sub>     | 6    | -    | 18   | V    |

| LIN operating voltage                                                           | V <sub>SUP_LIN</sub> | 7    | -    | 18   | V    |

| Supply Current Range                                                            |                      |      |      |      |      |

| NORMAL Mode                                                                     | I <sub>RUN</sub>     | -    | 14   | -    | mA   |

| STANDBY Mode                                                                    | I <sub>STBY</sub>    | -    | 10   | -    | mA   |

| SLEEP Mode (measured at $T_J=27^{\circ}C$ ; $V_{SUP}=13V$ through all VSS pins) | I <sub>SLEEP</sub>   | -    | -    | 80   | μA   |

| Switchable Analog Supply Voltage (to S_P pin)                                   |                      |      |      |      |      |

| Voltage range (S_P pin unloaded)                                                | V <sub>SP</sub>      | 4.5  | 5    | 5.5  | V    |

| Voltage range (S_P pin loaded with 5mA)                                         | $V_{SP_{5mA}}$       | 3.8  | 4.5  | 5.2  | V    |

| Nominal output current                                                          | I <sub>SP</sub>      | 0    | -    | 5    | mA   |

| Current limitation in case of short to GND                                      | I <sub>SP_OC</sub>   | 6    | -    | 9    | mA   |

| GPIO Supply Voltage                                                             |                      |      |      |      |      |

| Voltage range                                                                   | V <sub>GPIO</sub>    | 2.97 | 3.3  | 3.63 | V    |

| Charge Pump                                                          |                      |      |     |      |    |

|----------------------------------------------------------------------|----------------------|------|-----|------|----|

| Charge pump output voltage (with respect to VDDE1; drivers disabled) | V <sub>CP</sub>      | 4.5  | 5.0 | 5.5  | V  |

| Charge pump output current (through CAP_CP pin)                      | ICAP_CP              | -    | -   | 10   | μA |

| External Capacitor Pins Voltage                                      |                      |      |     |      |    |

| REG5V0 capacitor pin CAP_5V0                                         | V <sub>CAP_5V0</sub> | 4.5  | 5.0 | 5.5  | V  |

| REG3V3 capacitor pin CAP_3V3                                         | Vcap_3v3             | 2.97 | 3.3 | 3.63 | V  |

| REG1V8 capacitor pin CAP_1V8 (on SBC side)                           | V <sub>CAP_1V8</sub> | 1.62 | 1.8 | 1.98 | V  |

| REG1V8 capacitor pin CAP_MCU (on MCU side)                           | V <sub>CAP_MCU</sub> | 1.62 | 1.8 | 1.98 | V  |

| Charge pump capacitor pin CAP_CP (with respect to VDDE1 pin)         | V <sub>CAP_CP</sub>  | 4.3  | -   | 5.5  | V  |

## Table 1.5 System Resets and Supply Monitoring

| Parameter                                                                                                                                                                                     | Symbol                | Min.       | Тур. | Max. | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|------------|------|------|------|

| Power-On Reset                                                                                                                                                                                |                       |            |      |      |      |

| Threshold <sup>1)</sup>                                                                                                                                                                       | PORTH                 | 4.2        | 4.5  | 4.8  | V    |

| Hysteresis                                                                                                                                                                                    | PORHYST               | 0.2        | 0.3  | 0.4  | V    |

| Under-Voltage Detection                                                                                                                                                                       |                       |            |      |      |      |

| Threshold <sup>1)</sup>                                                                                                                                                                       | UVD <sub>TH</sub>     | 5.7        | 6.0  | 6.3  | V    |

| Hysteresis                                                                                                                                                                                    | UVD <sub>HYST</sub>   | 0.05       | 0.2  | 0.3  | V    |

| Over-Voltage Detection                                                                                                                                                                        |                       |            |      |      |      |

| Threshold <sup>1)</sup>                                                                                                                                                                       | OVD <sub>TH</sub>     | 17.7       | 18.6 | 19.5 | V    |

| Hysteresis                                                                                                                                                                                    | OVD <sub>HYST</sub>   | 0.3        | 0.5  | 0.7  | V    |

| Over-Temperature Drivers Shut-Down                                                                                                                                                            |                       |            |      |      |      |

| Threshold <sup>2)</sup>                                                                                                                                                                       | OVT <sub>TH</sub>     | -          | 125  | -    | °C   |

| Hysteresis <sup>2)</sup>                                                                                                                                                                      | OVT <sub>HYST</sub>   | -          | 5    | -    | °C   |

| <ol> <li>These parameters are defined with respect to the potential at the VDDE pin.</li> <li>Junction temperature of the SBC chip. Parameter guaranteed by process monitoring but</li> </ol> | t not tested during p | roduction. |      |      |      |

#### 1.2.2. Digital Interface (GPIOs)

Table 1.6

GPIO Electrical Characteristics

| Parameter                                             | Symbol              | Min. | Тур. | Max. | Unit |

|-------------------------------------------------------|---------------------|------|------|------|------|

| Input low voltage                                     | VIL                 | -0.3 | -    | 0.8  | V    |

| Input high voltage                                    | VIH                 | 2    | -    | 3.6  | V    |

| Schmitt Trigger Low to High Threshold Point           | V <sub>T+</sub>     | 1.4  | 1.5  | 1.6  | V    |

| Schmitt Trigger High to Low Threshold Point           | V <sub>T</sub> .    | 1.1  | 1.2  | 1.3  | V    |

| Input leakage current (at V <sub>I</sub> =3.3V or 0V) | I,                  | -1   | -    | 1    | μA   |

| Tri-state output leakage current (at VI =3.3V or 0V)  | l <sub>oz</sub>     | -1   | -    | 1    | μA   |

| Output low voltage                                    | V <sub>OL</sub>     | -    | -    | 0.4  | V    |

| Output high voltage                                   | V <sub>OH</sub>     | 2.4  | -    | -    | V    |

| Single GPIO source current                            | I <sub>SOURCE</sub> | -    | -    | 5    | mA   |

| Single GPIO sink current                              | I <sub>SINK</sub>   | -    | -    | 5    | mA   |

#### 1.2.3. LIN Physical Layer

**Note:** LIN parameters are specified for an ambient temperature range from -40°C to 125°C. Although the internal over-temperature protection might be activated due to device self-heating, LIN communication and MCU operation remain unaffected.

#### Table 1.7 LIN Electrical Parameters

Note: See important notes at end of table.

| Parameter                                          | Symbol                   | LIN Spec 2.2<br>Reference | Min   | Тур. | Мах   | Unit             |