### Description

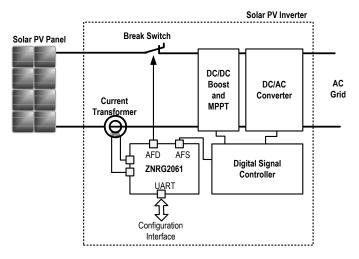

The ZNRG2061 is a smart system-on-chip for arc-fault detection in photovoltaic (PV) solar power systems. Its trainable algorithm delivers safe and reliable signaling of arc-faults while tolerating typical noise patterns present in solar power systems.

The algorithm continuously monitors the photovoltaic DC current and observes any current fluctuation, ultimately performing a fast Fourier transform (FFT) analysis. The frequency spectrum is compared to a previously memorized baseline. If the signature of an arc-fault is detected, a failure event is generated. To prevent nuisance tripping, the baseline and other criteria are determined with a training procedure. Training is initiated via the graphical user interface (GUI) configuration software.

In addition to a current transformer, which also acts as galvanic isolator from the primary high voltage, the ZNRG2061 system-onchip requires only a few external components. It contains all necessary data acquisition, signal conditioning, and DSP functions to provide reliable arc-fault signaling.

Self-diagnosis is performed continuously, ensuring that the device operates safely at all times.

To simplify design-in and accelerate future systems UL listings, the ZNRG2061 is designed in compliance with UL 1699B and recognized according to UL 1998.

# **Typical Applications**

Integrated arc-fault detection in

- PV solar power inverters

- Combiner boxes

- DC optimizers

- Stand-alone arc-fault circuit interrupters (AFCI)

### **Physical Characteristics**

- Operating temperature -40°C to 85°C

- Supply voltage 6V to 24V

- 32-PQFN package 5 × 5 × 0.9 mm

# **Available Support**

- Evaluation Kit

- Application Notes

### Features

- Complete DC line arc-fault detection solution in a single IC

- UL 1699B design compliant and UL 1988 recognized

- Advanced signal processing via FFT

- Small footprint package 5 × 5 mm compact package with only a few external components significantly contributes to optimized application's bill-of-materials (BOM) and circuit board area utilization

- Smart automated, trainable algorithm empowers system customization and adaptation to avoid nuisance tripping

- Signaling with a latched (static) and non-latched (dynamic) digital output

- Wide supply voltage range

- Built-in self-test

- Ability to interface with pseudo arc signal

- Automatic gain adjustment

- Fault clear from annunciator (via communication)

- UL recognition simplifies UL listing of the end product

# **Application Block Diagram**

# () IDT.

# Contents

| 1.  | Pin A              | Assignme   | nts                                         | 4  |  |  |  |  |

|-----|--------------------|------------|---------------------------------------------|----|--|--|--|--|

| 2.  |                    |            | ns                                          |    |  |  |  |  |

| 3.  |                    |            | mum Ratings                                 |    |  |  |  |  |

| 4.  |                    |            | d Operating Conditions                      |    |  |  |  |  |

| 5.  |                    |            | racteristics                                |    |  |  |  |  |

| 6.  | Theo               | ory of Ope | ration                                      | 9  |  |  |  |  |

|     | 6.1                |            | W                                           |    |  |  |  |  |

|     |                    | 6.1.1      | Arc Power                                   | 10 |  |  |  |  |

|     |                    | 6.1.2      | Selecting Spectral Frequencies for Analysis | 10 |  |  |  |  |

|     |                    | 6.1.3      | Post Filter                                 | 10 |  |  |  |  |

|     |                    | 6.1.4      | Training Sequence                           | 10 |  |  |  |  |

| 7.  | Outp               | ut Signal  | Description                                 | 11 |  |  |  |  |

|     | 7.1                | AFD – /    | Arc Fault Detector                          | 11 |  |  |  |  |

|     | 7.2                | AFS – /    | Arc Feature Signal                          | 11 |  |  |  |  |

| 8.  | Appli              | ication Ci | rcuit                                       | 12 |  |  |  |  |

| 9.  | Fail S             | Safe Ope   | ration                                      | 13 |  |  |  |  |

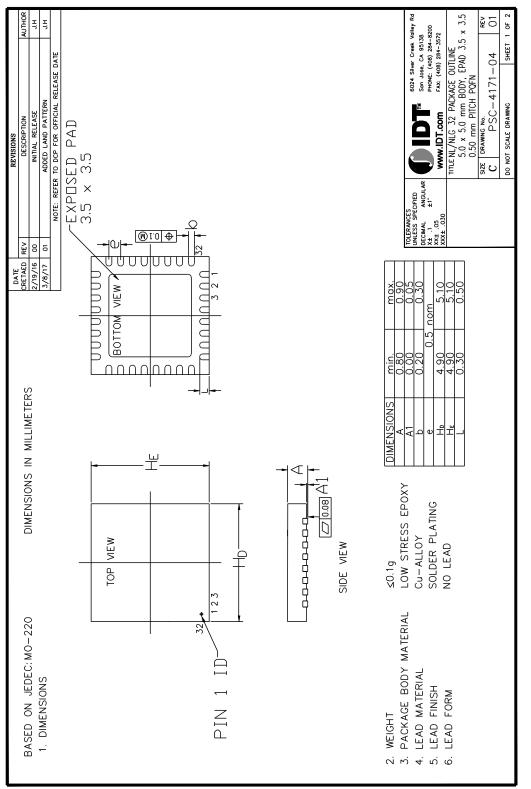

| 10. | Pack               | age Drav   | <i>v</i> ing                                | 14 |  |  |  |  |

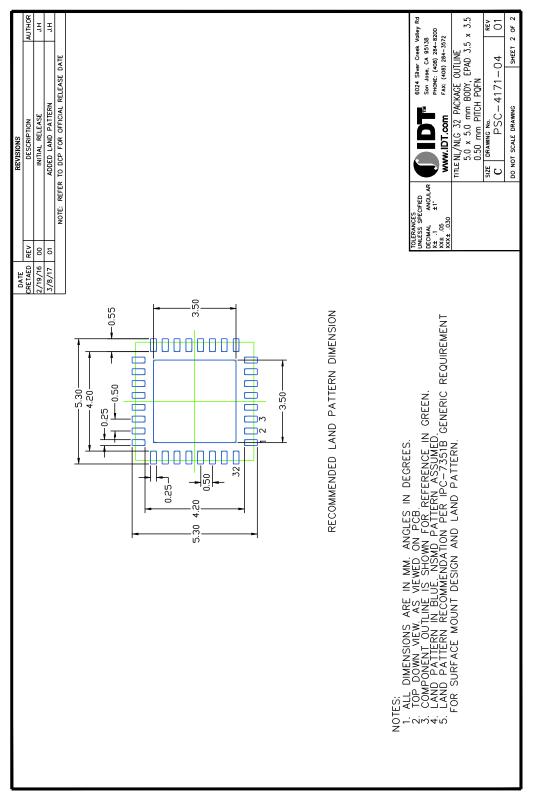

| 11. | Reco               | ommende    | d Land Pattern                              | 15 |  |  |  |  |

| 12. | Mark               | ing Diagr  | am                                          | 16 |  |  |  |  |

| 13. | Glos               | sary       |                                             | 16 |  |  |  |  |

| 14. | Orde               | ring Infor | mation                                      | 17 |  |  |  |  |

| 15. | Revision History17 |            |                                             |    |  |  |  |  |

# **List of Figures**

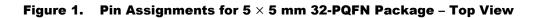

| Figure 1. | Pin Assignments for 5 × 5 mm 32-PQFN Package – Top View | 4  |

|-----------|---------------------------------------------------------|----|

| Figure 2. | Functional Description Diagram                          | 9  |

| Figure 3. | Output Signal Diagram                                   | 11 |

| Figure 4. | Input Circuit Schematic                                 | 12 |

| Figure 5. | Main Application Schematic                              | 12 |

| Figure 6. | 32-PQFN Package Drawing of the ZNRG2061                 | 14 |

| Figure 7. | 32-PQFN Landing Pattern                                 | 15 |

# **List of Tables**

| Table 1. | Pin Descriptions                          | 4  |

|----------|-------------------------------------------|----|

| Table 2. | ZNRG2061 Absolute Maximum Ratings         | 6  |

|          | ZNRG2061 Recommended Operating Conditions |    |

| Table 4. | ZNRG2061 Electrical Characteristics       | 7  |

| Table 5. | Tripping Time vs. Arc Power               | 10 |

### 1. Pin Assignments

### 2. Pin Descriptions

#### Table 1.Pin Descriptions

| Number | Name   | Туре           | Description                                                     |

|--------|--------|----------------|-----------------------------------------------------------------|

| 1      | VDD    | Supply         | Supply voltage.                                                 |

| 2      | GND    | Ground         | Analog/digital ground.                                          |

| 3      | GND    | Ground         | Analog/digital ground.                                          |

| 4      | CT1    | Analog Input   | Differential voltage input.                                     |

| 5      | CT2    | Analog Input   | Differential voltage input.                                     |

| 6      | GND    | Ground         | Analog/digital ground.                                          |

| 7      | VANA   | Analog Output  | VANA regulator output; external capacitance 470nF to board GND. |

| 8      | SENSLV | Analog Input   | Voltage sensing input.                                          |

| 9      | SENSGN | Analog Input   | Voltage sensing input.                                          |

| 10     | AFD    | Digital Output | Arc-fault detected; latched output.                             |

| 11     | AFS    | Digital Output | Arc feature signal; non-latched output.                         |

| Number         | Name   | Туре           | Description                                                     |

|----------------|--------|----------------|-----------------------------------------------------------------|

| 12             | RxD    | Output         | RxD. Pull-up to VPER via $4.7k\Omega$ resistor.                 |

| 13             | TxD    | Input          | TxD. Pull-down to GND via 4.7k $\Omega$ resistor.               |

| 14             | IO     | Unused         | Digital output.                                                 |

| 15             | NC     | Unused         | Unused. Pull up to VPER via $4.7k\Omega$ resistor.              |

| 16             | NC     | Unused         | Unused. Pull up to VPER via $4.7k\Omega$ resistor.              |

| 17             | GND    | Ground         | Analog/digital ground.                                          |

| 18             | NC     | Unused         | Unused. Pull up to VPER via $4.7k\Omega$ resistor.              |

| 19             | NC     | Unused         | Unused. Pull up to VPER via $4.7k\Omega$ resistor.              |

| 20             | NC     | Unused         | Unused. Pull up to VPER via $4.7k\Omega$ resistor.              |

| 21             | STO    | Digital Output | Safety trouble output.                                          |

| 22, 23         | NC     | Unused         | Unused. Leave unconnected.                                      |

| 24             | GND    | Ground         | Analog/digital ground.                                          |

| 25             | NC     | Unused         | Unused. Leave unconnected.                                      |

| 26             | VDIG   | Analog Output  | VDIG regulator output; external capacitance 10nF to board GND.  |

| 27             | GND    | Ground         | Analog/digital ground.                                          |

| 28             | TEST   | Digital IO     | Unused. Leave unconnected.                                      |

| 29             | VCOR   | Analog Output  | VCOR regulator output; external capacitance 2.2µF to board GND. |

| 30             | VPER   | Analog Output  | VPER regulator output; external capacitance 2.2µF to board GND. |

| 31             | VOTP   | Supply         | OTP supply voltage input.                                       |

| 32             | SENSHV | Analog Input   | Voltage sensing input.                                          |

| Exposed<br>Pad | GND    | Ground         | Analog/digital ground.                                          |

### 3. Absolute Maximum Ratings

The absolute maximum ratings are stress ratings only. Stresses greater than those listed below can cause permanent damage to the device. Functional operation of the ZNRG2061 at absolute maximum ratings is not implied. Exposure to absolute maximum rating conditions might affect device reliability.

Table 2.

ZNRG2061 Absolute Maximum Ratings

| No      | Parameter                      | Symbol              | Conditions | Min                    | Мах                    | Unit |

|---------|--------------------------------|---------------------|------------|------------------------|------------------------|------|

| 3.1.1.  | External power supply          | V <sub>DD</sub>     |            | V <sub>GND</sub> - 0.3 | 40                     | V    |

| 3.1.2.  | Current sensing, CT1 pin       | V <sub>CT1</sub>    |            | V <sub>GND</sub> - 0.3 | V <sub>ANA</sub> + 0.3 | V    |

| 3.1.3.  | Current sensing, CT2 pin       | V <sub>CT2</sub>    |            | V <sub>GND</sub> - 0.3 | V <sub>ANA</sub> + 0.3 | V    |

| 3.1.4.  | Voltage sensing, SENSHV pin    | V <sub>SENSHV</sub> |            | 0                      | 33                     | V    |

| 3.1.5.  | Voltage sensing, SENSLV pin    | V <sub>SENSLV</sub> |            | V <sub>GND</sub> - 0.3 | V <sub>ANA</sub> + 0.3 | V    |

| 3.1.6.  | Voltage sensing, SENSGN        | V <sub>SENSGN</sub> |            | V <sub>GND</sub> - 0.3 | V <sub>ANA</sub> + 0.3 | V    |

| 3.1.7.  | AFD pin                        | V <sub>AFD</sub>    |            | V <sub>GND</sub> - 0.3 | V <sub>PER</sub> + 0.3 | V    |

| 3.1.8.  | AFS pin                        | V <sub>AFS</sub>    |            | V <sub>GND</sub> - 0.3 | V <sub>PER</sub> + 0.3 | V    |

| 3.1.9.  | RxD pin                        | V <sub>RxD</sub>    |            | V <sub>GND</sub> - 0.3 | V <sub>PER</sub> + 0.3 | V    |

| 3.1.10. | TxD pin                        | V <sub>TxD</sub>    |            | V <sub>GND</sub> - 0.3 | V <sub>PER</sub> + 0.3 | V    |

| 3.1.11. | IO pin                         | V <sub>IO</sub>     | Reserved   | V <sub>GND</sub> - 0.3 | V <sub>PER</sub> + 0.3 | V    |

| 3.1.12. | Ambient temperature under bias | T <sub>A</sub>      |            |                        | 125                    | °C   |

| 3.1.13. | Junction temperature           | Tj                  |            |                        | 135                    | °C   |

| 3.1.14. | Storage temperature            | Ts                  |            | -50                    | 125                    | °C   |

# 4. Recommended Operating Conditions

Table 3.

ZNRG2061 Recommended Operating Conditions

| No.    | Parameter                   | Symbol          | Conditions               | Min                    | Тур | Max                    | Unit |

|--------|-----------------------------|-----------------|--------------------------|------------------------|-----|------------------------|------|

| 4.1.1. | Operating temperature range | T <sub>A</sub>  | Ambient,<br>RTHP = 35K/W | -40                    |     | 85                     | °C   |

| 4.1.2. | Supply voltage at VDD pin   | $V_{\text{DD}}$ |                          | 6                      |     | 24                     | V    |

| 4.1.3. | Digital input voltage LOW   | V <sub>IL</sub> |                          | 0                      |     | 0.3 * V <sub>PER</sub> | V    |

| 4.1.4. | Digital input voltage HIGH  | VIH             |                          | 0.7 * V <sub>PER</sub> |     | V <sub>PER</sub>       | V    |

### 5. Electrical Characteristics

#### Table 4. ZNRG2061 Electrical Characteristics

| No.       | Parameter                                                         | Symbol                    | Conditions            | Min                 | Тур      | Max                          | Unit |

|-----------|-------------------------------------------------------------------|---------------------------|-----------------------|---------------------|----------|------------------------------|------|

| Supply    |                                                                   | •                         |                       |                     | L        |                              |      |

| 5.1.1.    | Average supply current at VDD                                     | I <sub>DD_avg</sub>       |                       |                     | 20       |                              | mA   |

| 5.1.2.    | Average power dissipation                                         | P <sub>DD_avg</sub>       |                       |                     | 240      |                              | mW   |

| 5.1.3.    | Internal analog power supply voltage                              | V <sub>ANA</sub>          |                       | 2.4                 | 2.5      | 2.6                          | V    |

| 5.1.4.    | Internal digital and RAM power supply voltage                     | V <sub>DIG</sub>          |                       | 1.62                | 1.8      | 1.98                         | V    |

| 5.1.5.    | Internal power supply voltage for microcontroller unit (MCU) core | V <sub>COR</sub>          |                       | 1.62                | 1.8      | 1.98                         | V    |

| 5.1.6.    | Internal power supply voltage (periphery)                         | V <sub>PER</sub>          |                       | 2.97                | 3.3      | 3.63                         | V    |

| Primary   | ADC Channel                                                       | ·                         |                       |                     |          |                              |      |

| 5.2.1.    | Input signal range <sup>[a]</sup>                                 | Range <sub>CT</sub>       | -3                    |                     |          | 300                          | mV   |

| 5.2.2.    | Input leakage current <sup>[a]</sup>                              | I <sub>LEAK_C</sub>       | T <sub>A</sub> = 25°C | -3                  |          | +3                           | nA   |

| Auxiliary | / ADC Channel                                                     |                           |                       |                     | <u>I</u> |                              |      |

| 5.3.1.    | Input signal range SENSHV <sup>[a]</sup>                          | V <sub>SENSHV</sub>       |                       | 0                   |          | 28.8                         | V    |

| 5.3.2.    | Input signal range SENSLV <sup>[a]</sup>                          | V <sub>SENSLV</sub>       |                       | V <sub>SENSGN</sub> |          | V <sub>SENSGN</sub><br>+ 1.2 | V    |

| 5.3.3.    | Input signal range SENSGN <sup>[a]</sup>                          | V <sub>SENSGN</sub>       |                       | 0                   |          | 1.2                          | V    |

| Power-o   | n Reset (POR)                                                     |                           |                       | <u></u>             | I        | •                            |      |

| 5.4.1.    | Power-on reset                                                    | V <sub>PORB</sub>         | At V <sub>DD</sub>    | 2.75                | 3.0      | 3.6                          | V    |

| 5.4.2.    | Power-on-reset hysteresis                                         | Hyst <sub>PORB</sub>      | At V <sub>DD</sub>    |                     | 300      |                              | mV   |

| 5.4.3.    | Low-voltage flag                                                  | low_voltage               | At V <sub>DD</sub>    | 1.8                 | 2.0      | 2.3                          | V    |

| 5.4.4.    | V <sub>VPER</sub> high <sup>[a]</sup>                             | VPER_high                 | At V <sub>DD</sub>    | 3.9                 | 4.05     | 4.2                          | V    |

| 5.4.5.    | V <sub>VPER</sub> high hysteresis <sup>[a]</sup>                  | Hyst <sub>VPER_high</sub> | At V <sub>DD</sub>    |                     | 400      |                              | mV   |

| Oscillato | br                                                                | •                         | •                     |                     | ·        | •                            |      |

| 5.5.1.    | Frequency                                                         | f <sub>HPO</sub>          |                       |                     | 20       |                              | MHz  |

| 5.5.2.    | Accuracy (including temperature drift) <sup>[a]</sup>             |                           |                       | -1                  |          | 1                            | %    |

|           | ÷                                                                 | •                         | •                     |                     | •        |                              |      |

| No.      | Parameter                                                      | Symbol             | Conditions                 | Min      | Тур | Max | Unit |

|----------|----------------------------------------------------------------|--------------------|----------------------------|----------|-----|-----|------|

| Microco  | ntroller Platform                                              |                    |                            | <u> </u> |     |     |      |

| 5.6.1.   | MCU start-up time after POR <sup>[a]</sup>                     |                    |                            |          | 80  |     | μs   |

| 5.6.2.   | MCU start-up time<br>after Standby Mode wake up <sup>[a]</sup> |                    |                            |          | 1   |     | μs   |

| Functior | nal Timing                                                     |                    |                            |          |     |     |      |

| 5.7.1.   | AFD maximum trip time <sup>[b]</sup>                           | t <sub>MTT</sub>   |                            |          |     | 800 | ms   |

| 5.7.2.   | AFD complete calculation time                                  | t <sub>CCT</sub>   |                            |          |     | 700 | ms   |

| 5.7.3.   | AFD single arc calculation loop                                | t <sub>SACL</sub>  | Not in command mode        |          |     | 40  | ms   |

| 5.7.4.   | Start-up built-in self-test                                    | t <sub>SBIST</sub> |                            |          |     | 200 | ms   |

| 5.7.5.   | Communication frame response                                   | t <sub>CFR</sub>   | Confirm with product valid |          |     | 40  | ms   |

| 5.7.6.   | Transport protocol timeout                                     | t <sub>TPT</sub>   |                            |          |     | 100 | ms   |

| 5.7.7.   | Command mode timeout                                           | t <sub>CMT</sub>   |                            |          |     | 5   | min  |

| Electros | tatic Discharge                                                |                    |                            |          |     |     |      |

| 5.8.1.   | ESD on system level [c]                                        |                    | IEC61000-4-2               |          |     | ±2  | kV   |

| 5.8.2.   | ESD, SENSHV on system level                                    |                    | IEC61000-4-2               |          |     | ±2  | kV   |

[a] Not tested in production test. Given by design and/or characterization.

[b] Combined system of AFD + external relay.

[c] With external protection diode GSOT36.

# 6. Theory of Operation

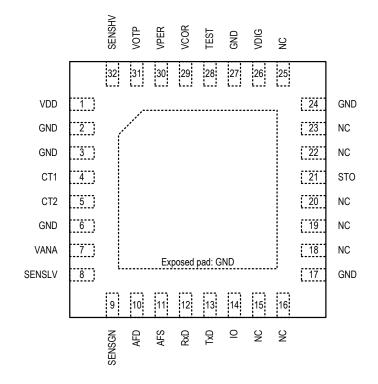

### 6.1 Overview

The DC current of solar installations contains specific noise patterns, some of which are due to potentially dangerous arcing events, while others have no potentially dangerous consequence. The latter noise originates from typical sources like inverters, maximum power point tracker (MPPT) optimization, changing exposure of solar panels to the sun, and load changes at the output of the inverter, which are all multiplied by parasitic capacitive and inductive components of wiring and connectors.

The main current is sensed through a current transformer that also provides galvanic isolation. The number of turns on the current transformer must be chosen such that the maximum AC output voltage is lower than  $\pm 300$  mVp. The signal from the current transformer is fed into an external low-pass filter before reaching the input pins of the IC. The cutoff frequency of the filter should be 16kHz.

The primary current is subsequently pre-amplified and converted into a digital bit stream by a 24-bit sigma-delta analog-to-digital converter (ADC). The time domain signal is then fed into an FFT block that provides a representation of the primary current in the frequency domain. A microcontroller analyzes the FFT data for both level and duration of selected spectral frequency bands to provide reliable detection of potential hazardous arc conditions. There is a trade-off between the fastest possible detection time and achieving minimal probability of false positive alarms. UL's 1699B standard was used as a reference for detection time. The ZNRG2061 is designed such that the detector output reacts 100 milliseconds faster than the limits in the UL standard, leaving sufficient time for the customer's system to react to the arc detector signal.

Upon detecting an arc fault, the digital output pin AFD is set with a built-in latch function. AFD can be reset only by interrupting the supply (power-on reset). The alternative output signal AFS digitally indicates whenever arc-like features have been detected in the current flow. This output resets itself as soon as the suspicious current characteristics have disappeared. See section 7 for details.

#### Figure 2. Functional Description Diagram

#### 6.1.1 Arc Power

The power of the arc determines the maximum tripping time allowed. The higher the arc power, the shorter the allowed time before the arc detection alarm output is set. The tripping time is a sum of the detection time from the ZNRG2061 and the time for the external circuit (relay) to react accordingly.

#### Table 5.Tripping Time vs. Arc Power

Note: The following specifications are from Underwriters Laboratory's document UL 1699B: Outline of Investigation for Photovoltaic (PV) DC Arc-Fault Circuit Protection.

| Arc Power (Watts)           | 300W | 500W | 650W | 900W |

|-----------------------------|------|------|------|------|

| Maximum tripping time (sec) | 2    | 1.5  | 1.2  | 0.8  |

Since power is not measured, ZNRG2061 will respond within less than 700ms, meeting the worst case of 800ms system's margin, as required by UL.

#### 6.1.2 Selecting Spectral Frequencies for Analysis

The user can select a particular spectral range of interest. The range is defined by two frequencies, LOW and HIGH. All of the spectral bins between these two frequencies are the only frequencies selected for further analysis. Note that the choice of the low/high frequency is not random; they must correspond to existing frequencies in the discrete spectra. Alternatively, they can be defined as the index number from 0 to 127 in a FFT of 256 frequency bins. Refer to the *ZNRG2061 AFD GUI User Manual*.

#### 6.1.3 Post Filter

A post filter is implemented in order to avoid false triggering by spikes, noises, or short time relay effects. The post filter counts the number of consecutively detected arcs. This filter defines the minimum duration of an arc before it triggers the "arc detected" alarm output. The post filter value is compared against a pre-programmed threshold.

#### 6.1.4 Training Sequence

Refer to the ZNRG2061 Functional Safety Manual for the training sequence.

### 7. Output Signal Description

Figure 3 illustrates the signal behavior for the AFD and AFS signals under various conditions.

#### Figure 3. Output Signal Diagram

|      | No Power  | Power up |   | Noise |      | A    | rc |      | Chip | Malfur | nction |  |

|------|-----------|----------|---|-------|------|------|----|------|------|--------|--------|--|

| VDDE |           |          |   |       | <br> | <br> |    | <br> |      |        |        |  |

| AFD  | undefined |          | 1 |       |      |      |    |      |      |        |        |  |

| AFS  | undefined |          |   |       |      |      |    |      |      |        |        |  |

### 7.1 AFD – Arc Fault Detector

AFD is a static pin, which can be used to directly control a DC break switch. If an arc is detected, the AFD output level goes high.

If the built-in self-test (BIST) detects a malfunction, the AFD will be set to high as well. In the event of a malfunction, the device might attempt to recover automatically. However, the AFD will be set to HIGH if the final recovery attempt is not successful.

Once set, the AFD pin is latched (permanently set) HIGH and the device will not reset the output by itself. Only a power off/on cycle or a GUI command can reset this pin.

### 7.2 AFS – Arc Feature Signal

AFS is a dynamic pin, which outputs a signal similar to pulse width modulation (PWM). The information on AFS is defined by the width (in ms) of the positive pulse width. It has three clearly distinguishable states:

- PWMe: Error and/or failure

Pulse width < 10ms (or permanent 0V) or pulse width > 40ms (or permanent 3.3V)

- PWMn: There is no ARC and no failure Pulse width of 16ms to 18ms

- PWMa: There is ARC and/or failure Pulse width of 32ms to 34ms

This pin can be used for the following purposes:

- The AFS can serve as secondary validation pin. This can be implemented on a system level. The AFS pin is made to be complementary (dynamic vs. static) to the AFD pin, so that there is an opportunity for detecting a complete component failure.

- The AFS output can be used to indicate an error condition as part of its normal functions. It will stop its PWM-like pulses if a malfunction is detected. Thus a small external circuit (watchdog for example) can be used to display the state on an LED.

Example: In the unlikely case of a ZNRG2061 malfunction during an arcing event, the AFD might not be triggered. In this case, the AFS pin will remain static HIGH or LOW (PWM 0% or 100%) thus indicating the error.

### 8. Application Circuit

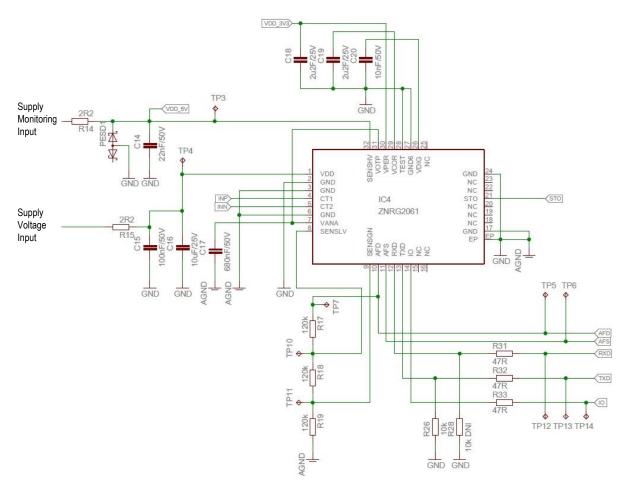

The typical application circuits in Figure 4 and Figure 5 are implemented in the ZNRG2061 Evaluation Board included in the ZNRG2061 Evaluation Kit (see section 14).

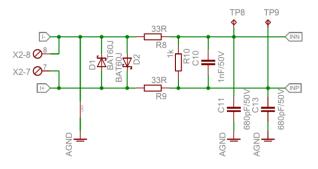

Figure 4. Input Circuit Schematic

Input terminals I+ and I- are directly fed from the current transformer. The output voltage of the current transformer is limited by D1 and D2 to their forward voltage drop of 0.32V maximum. The filter formed by R8, R9, R10 and C10, C11, C13 has a cut off frequency of 16kHz.

For more details on interfacing with a pseudo arc signal, refer to the ZNRG2061 Evaluation Kit User Manual.

### 9. Fail Safe Operation

Self-diagnostic and supervisory software are implemented within ZNRG2061. These functions rely on the close cooperation between the smart built in self-test (BIST) software and the hardware diagnostics block. The primary role of the BIST is to detect a malfunction occurring during run-time. Secondarily, the BIST will place the device into the Safe State and properly signal the malfunction if a malfunction is detected.

In normal operation mode, the device state is monitored using the AFD and AFS pins. However, the STO pin can be monitored in cases where high reliability is needed.

The STO (Safety Troubles Output) can be used as an indication of a severe malfunction. This output will be driven to HIGH when the reset of the system has finished. From this point forward, the STO pin will remain HIGH until the power down of the device. Any falling slope of the STO (high to low transition) is an indication of a malfunction occurring.

This enables the two following distinguishable situations:

- Low pulse. This indicates that the device has detected a failure and has gone into the Safe State. Functionality after this point might not be available.

- Permanent LOW. Complete device destruction might have occurred. If a very high level of reliability is needed from the system, the supply

voltage can be monitored (by an external MCU for example) as well. In this case, a LOW level at the STO pin and a high supply is an

indication of this hypothetical case.

In the event of a hardware malfunction, the normal outputs might not be functioning properly. The STO pin can be very useful in the case of a double fault of the AFD and the AFS outputs.

### **10. Package Drawing**

### **11. Recommended Land Pattern**

#### Figure 7. 32-PQFN Landing Pattern

# **12. Marking Diagram**

- 1. Line 1 is the company name.

- 2. Line 2 is the product name.

- 3. Line 3 is the lot number: XXXXXXX (see purchase order, not the engraved lot number)

- 4. Line 4 is the date code. "YYWW" is the last two digits of the year followed by two digits for the week that the part was assembled.

- 5. Line 5 is the UL logo.

### **13. Glossary**

| Acronym | Definition                                  |

|---------|---------------------------------------------|

| ADC     | Analog-to-Digital Converter                 |

| AFCI    | Arc-Fault Circuit Interrupter               |

| AFD     | Arc-Fault Detector/Detected                 |

| AFS     | Arc Feature Signal                          |

| BIST    | Built-in Self-Test                          |

| BOM     | Bill of Materials                           |

| FFT     | Fast Fourier Transform                      |

| GUI     | Graphical User Interface                    |

| LED     | Light Emitting Diode                        |

| MCU     | Microcontroller Unit                        |

| MPPT    | Maximum Power Point Tracker                 |

| PCB     | Printed Circuit Board                       |

| PGA     | Programmable Gain Amplifier                 |

| POR     | Power-on Reset                              |

| PV      | Photovoltaic                                |

| PWM     | Pulse Width Modulation                      |

| RTHP    | Thermal Resistance of the Package           |

| STO     | Safety Troubles Output                      |

| UART    | Universal Asynchronous Receiver/Transmitter |

### **14. Ordering Information**

| Orderable Part Number | Description and Package                                                                                                                                                                                                                                         | MSL Rating | Shipping Packaging | Temperature    |

|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|--------------------|----------------|

| ZNRG2061AA1R          | ZNRG2061 Arc-Fault Detector IC $5 \times 5 \text{ mm } 32\text{-}PQFN$                                                                                                                                                                                          | 3          | Reel               | -40°C to +85°C |

| ZNRG2061AA1V          | ZNRG2061 Arc-Fault Detector IC $5 \times 5$ mm 32-PQFN                                                                                                                                                                                                          | 3          | Tray               | -40°C to +85°C |

| ZNRG2061KITV1P0       | ZNRG2061 Evaluation Kit: Modular Evaluation Board for ZNRG2061, 100:100-turns current transformer, and micro-USB cable. Software and documentation can be downloaded from the product page at <a href="https://www.IDT.com/ZNRG2061">www.IDT.com/ZNRG2061</a> . |            |                    |                |

### **15. Revision History**

| Revision Date  | Description of Change                                            |  |

|----------------|------------------------------------------------------------------|--|

| March 31, 2017 | Correction for description of shipping package for ZNRG2061AA1V. |  |

| March 29, 2017 | Update for part codes and kit contents.                          |  |

| March 16, 2017 | Initial release of datasheet.                                    |  |

Corporate Headquarters 6024 Silver Creek Valley Road San Jose, CA 95138 www.IDT.com

#### Sales

1-800-345-7015 or 408-284-8200 Fax: 408-284-2775 www.IDT.com/go/sales

#### **Tech Support**

www.IDT.com/go/support

DISCLAIMER Integrated Device Technology, Inc. (IDT) and its affiliated companies (herein referred to as "IDT") reserve the right to modify the products and/or specifications described herein at any time, without notice, at IDT's sole discretion. Performance specifications and operating parameters of the described products are determined in an independent state and are not guaranteed to perform the same way when installed in customer products. The information contained herein is provided without representation or warranty of a ny kind, whether express or implied, including, but not limited to, the suitability of IDT's products for any particular purpose, an implied warranty of merchantability, or non-infringement of the intellectual property rights of others. This document is presented only as a guide and does not convey any license under intellectual property rights of IDT or any third parties.

IDT's products are not intended for use in applications involving extreme environmental conditions or in life support systems or similar devices where the failure or malfunction of an IDT product can be reasonably expected to significantly affect the health or safety of users. Anyone using an IDT product in such a manner does so at their own risk, absent an express, written agreement by IDT.

Integrated Device Technology, IDT and the IDT logo are trademarks or registered trademarks of IDT and its subsidiaries in the United States and other countries. Other trademarks used herein are the property of IDT or their respective third party owners. For datasheet type definitions and a glossary of common terms, visit www.idt.com/go/glossary. All contents of this document are copyright of Integrated Device Technology, Inc. All rights reserved.