Order

Now

Texas Instruments

bq25703A SLUSCU1 - MAY 2017

# bg25703A I2C Multi-Chemistry Battery Buck-Boost Charge Controller With System Power Monitor and Processor Hot Monitor

#### Features 1

- Charge 1- to 4-Cell Battery From Wide Range of Input Sources

- 3.5-V to 24-V Input Operating Voltage

- Supports USB2.0, USB 3.0, USB 3.1 (Type C), and USB\_PD Input Current Settings

- Seamless Transition Between Buck and Boost Operation

- Input Current and Voltage Regulation (IDPM) and VDPM) Against Source Overload

- Power/Current Monitor for CPU Throttling

- Comprehensive PROCHOT Profile, IMVP8 Compliant

- Input and Battery Current Monitor

- System Power Monitor, IMVP8 Compliant

- Narrow-VDC (NVDC) Power Path Management

- Instant-On With No Battery or Deeply **Discharged Battery**

- Battery Supplements System When Adapter is Fully-Loaded

- Ideal Diode Operation in Supplement Mode

- Power Up USB Port From Battery (USB OTG)

- Output 4.48-V to 20.8-V Compatible With USB PD

- Output Current Limit up to 6.35 A

- 800-kHz or 1.2-MHz Programmable Switching Frequency for 1-µH to 2.2-µH Low Profile Inductor

- Host Control Interface for Flexible System Configuration

- I2C (bq25703A) Port for Optimal System Performance and Status Reporting

- Hardware Pin to Set Input Current Limit \_ Without EC Control

- High Accuracy Regulation and Monitor

- ±0.5% Charge Voltage Regulation

- ±2% Input/Charge Current Regulation

- ±2% Input/Charge Current Monitor

- ±5% Power Monitor

- Safety

- Thermal Shutdown

- Input, System, Battery Overvoltage Protection

- MOSFET Inductor Overcurrent Protection

- Low Battery Quiescent Current

- Input Current Optimizer (ICO) to Extract Max Input • Power

- Charge Any Battery Chemistry: Li+, LiFePO4, NiCd, NiMH, Lead Acid

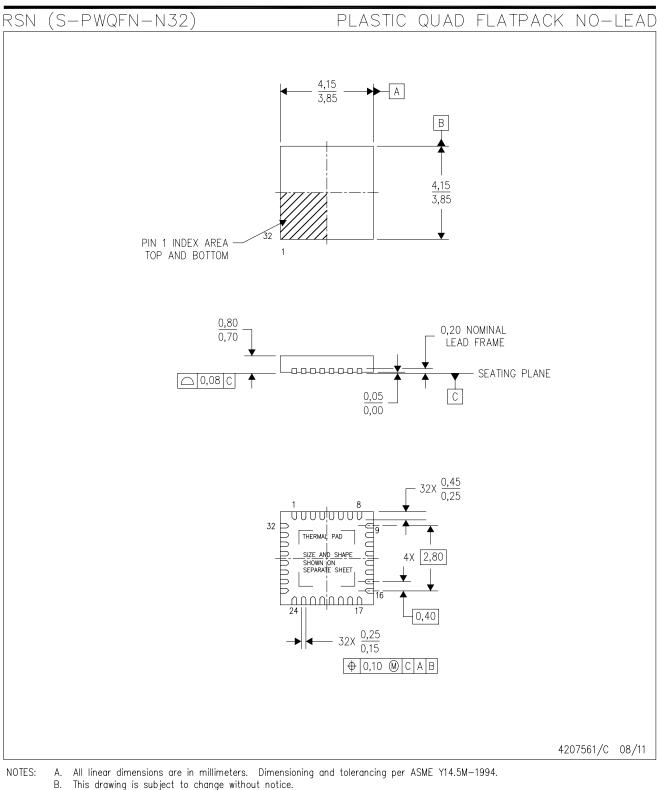

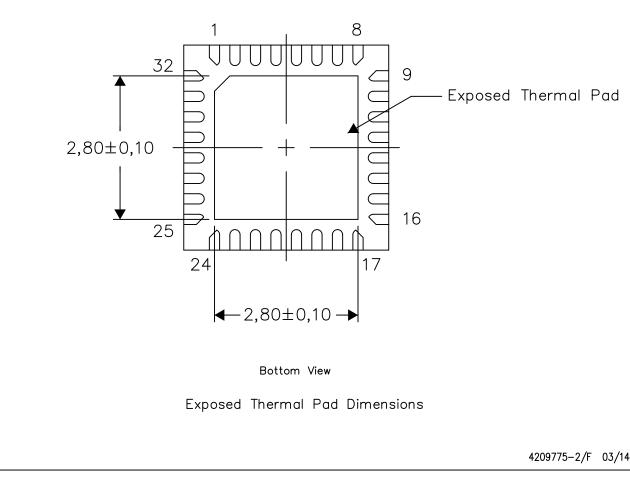

- Package: 32-Pin 4 × 4 WQFN

#### 2 Applications

- Drones, Bluetooth Speakers, IP Cameras, • Detachable, and Tablet PCs and Power Bank

- Industrial and Medical Equipment

- Portable Equipment With Rechargeable Batteries

## 3 Description

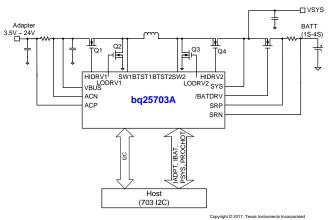

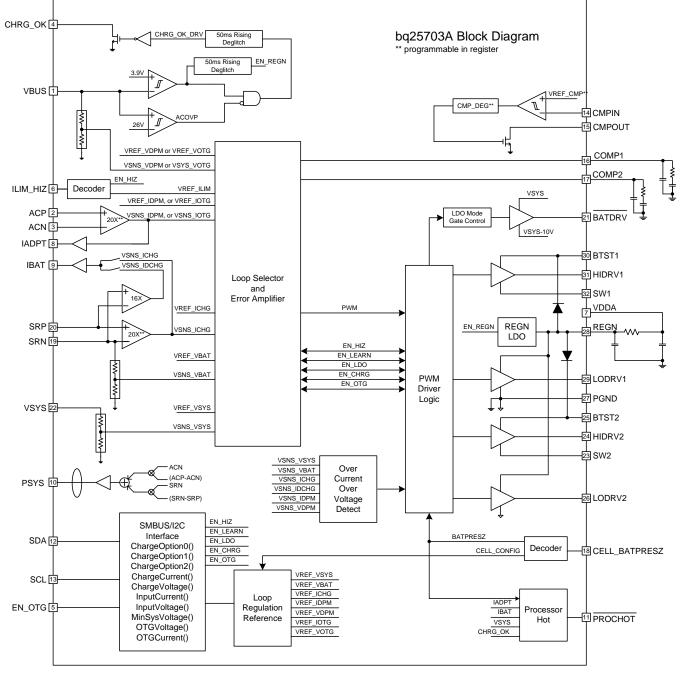

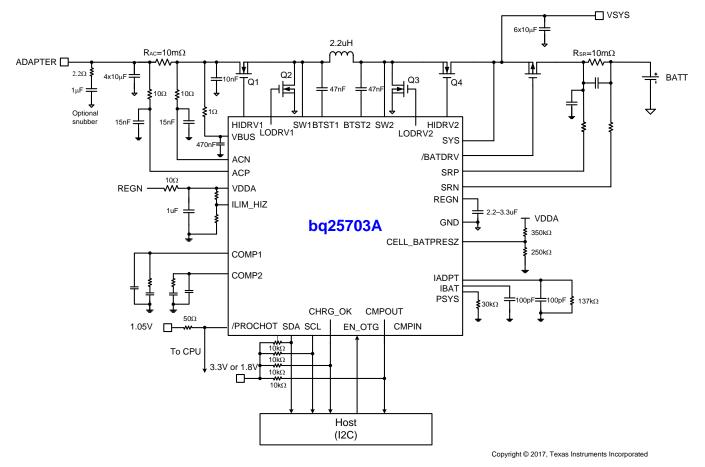

The bg25703A is a synchronous NVDC battery buckboost charge controller, offering low component count, high efficiency solution for space-constraint, multi-chemistry battery charging applications.

The NVDC-1 configuration allows the system to be regulated at battery voltage, but not drop below system minimum voltage. The system keeps operating even when the battery is completely discharged or removed. When load power exceeds input source rating, the battery goes into supplement mode and prevents the input source from being overloaded.

The bg25703A charges battery from a wide range of input sources including USB adapter, high voltage USB PD sources and traditional adapters.

| Device | Information | (1) |

|--------|-------------|-----|

|--------|-------------|-----|

| PART NUMBER | PACKAGE   | BODY SIZE (NOM)   |

|-------------|-----------|-------------------|

| bq25703A    | WQFN (32) | 4.00 mm × 4.00 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

## **Application Diagram**

An IMPORTANT NOTICE at the end of this data sheet addresses availability, warranty, changes, use in safety-critical applications, intellectual property matters and other important disclaimers. PRODUCTION DATA.

Texas Instruments

#### www.ti.com

# **Table of Contents**

| 1 | Feat | tures                            | 1               |

|---|------|----------------------------------|-----------------|

| 2 | Арр  | lications                        | 1               |

| 3 | Des  | cription                         | 1               |

| 4 | Rev  | ision History                    | 2               |

| 5 | Des  | cription (Continued)             | 3               |

| 6 | Pin  | Configuration and Functions      | 4               |

| 7 | Spe  | cifications                      | 7               |

|   | 7.1  | Absolute Maximum Ratings         | 7               |

|   | 7.2  | ESD Ratings                      | 7               |

|   | 7.3  | Recommended Operating Conditions | 7               |

|   | 7.4  | Thermal Information              | 8               |

|   | 7.5  | Electrical Characteristics       | 8               |

|   | 7.6  | Timing Requirements              | 16              |

|   | 7.7  | Typical Characteristics          | 17              |

| 8 | Deta | ailed Description                | 20              |

|   | 8.1  | Overview                         | 20              |

|   | 8.2  | Functional Block Diagram         | 21              |

|   | 8.3  | Feature Description              | <mark>22</mark> |

|   | 8.4  | Device Functional Modes          | 28              |

|   |      |                                  |                 |

|    | 8.5  | Programming 29                                     |

|----|------|----------------------------------------------------|

|    | 8.6  | Register Map 32                                    |

| 9  | App  | lication and Implementation                        |

|    | 9.1  | Application Information                            |

|    | 9.2  | Typical Application                                |

| 10 | Pow  | ver Supply Recommendations74                       |

| 11 |      | out                                                |

|    | 11.1 | Layout Guidelines75                                |

|    | 11.2 | Layout Example 75                                  |

| 12 | Dev  | ice and Documentation Support                      |

|    | 12.1 | Device Support                                     |

|    | 12.2 | Documentation Support 77                           |

|    | 12.3 | Receiving Notification of Documentation Updates 77 |

|    | 12.4 | Community Resources                                |

|    | 12.5 | Trademarks                                         |

|    | 12.6 | Electrostatic Discharge Caution 77                 |

|    | 12.7 | Glossary                                           |

| 13 | Mec  | hanical, Packaging, and Orderable                  |

|    |      | mation                                             |

|    |      |                                                    |

## 4 Revision History

| DATE     | REVISION | NOTES            |

|----------|----------|------------------|

| May 2017 | *        | Initial release. |

## **5** Description (Continued)

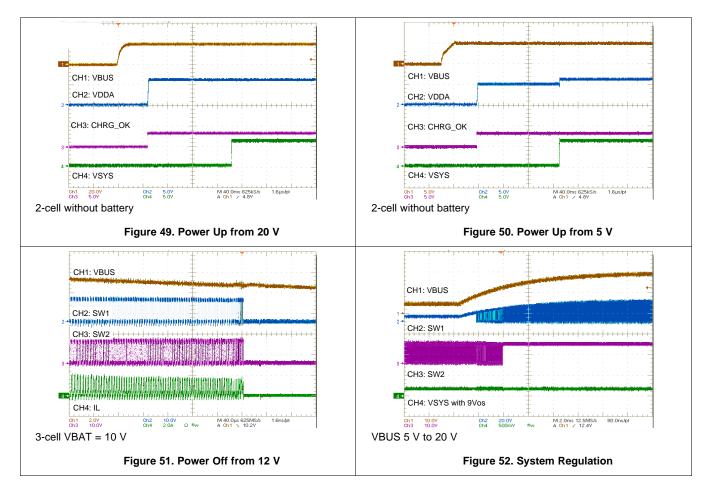

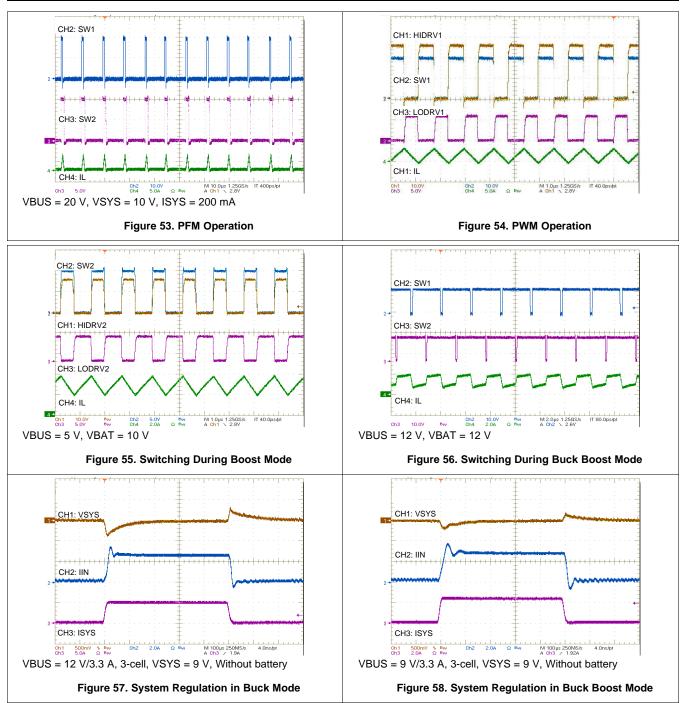

During power up, the charger sets converter to buck, boost or buck-boost configuration based on input source and battery conditions. The charger automatically transits among buck, boost and buck-boost configuration without host control.

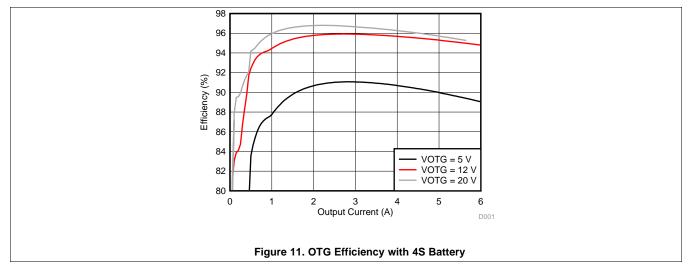

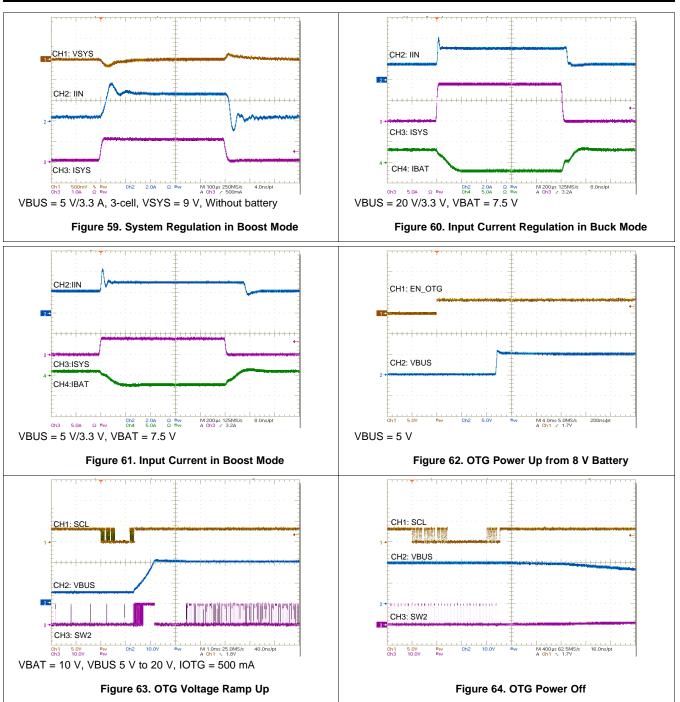

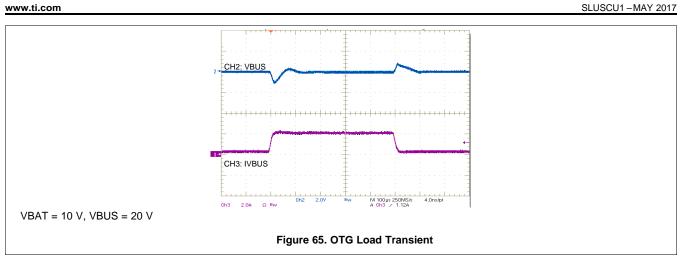

In the absence of an input source, the bq25703A supports On-the-Go (OTG) function from 1- to 4-cell battery to generate 4.48 V to 20.8 V on VBUS. During OTG mode, the charger regulates output voltage and output current.

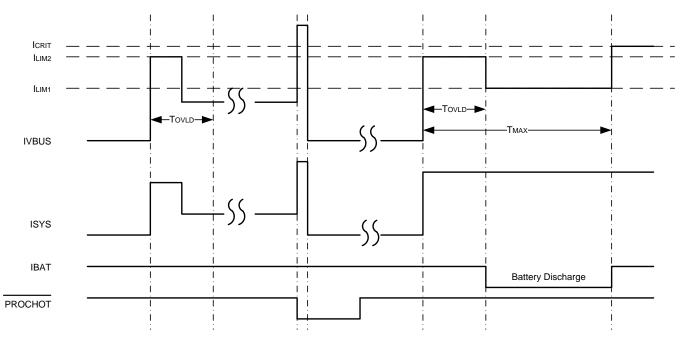

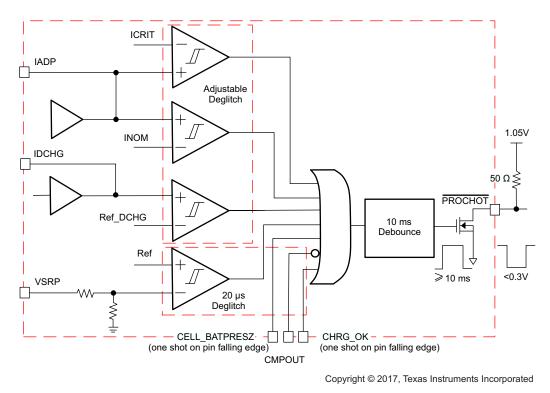

The bq25703A monitors adapter current, battery current and system power. The flexibly programmed PROCHOT output goes directly to CPU for throttle back when needed.

bq25703A SLUSCU1-MAY 2017 Texas INSTRUMENTS

www.ti.com

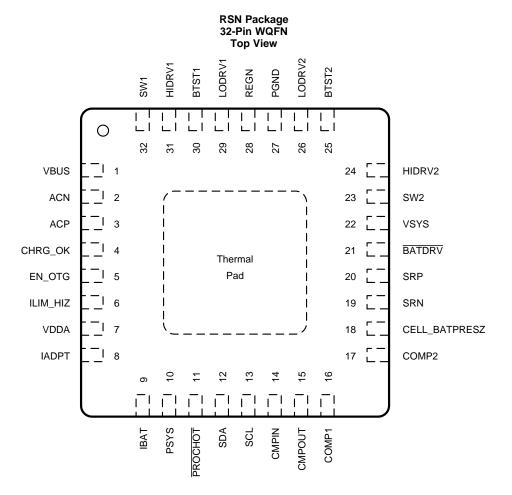

## 6 Pin Configuration and Functions

#### **Pin Functions**

| PIN           |        | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|---------------|--------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | NUMBER | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                |  |  |

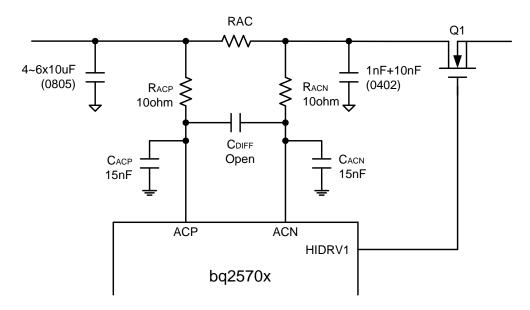

| ACN           | 2      | PWR | Input current sense resistor negative input. The leakage on ACP and ACN are matched. The series resistors on the ACP and ACN pins are placed between sense resistor and filter cap. Refer to <i>Application and Implementation</i> for ACP/ACN filter design.                                                                                                                              |  |  |

| ACP           | 3      | PWR | Input current sense resistor positive input. The leakage on ACP and ACN are matched. The series resistors on the ACP and ACN pins are placed between sense resistor and filter cap. Refer to <i>Application and Implementation</i> for ACP/ACN filter design.                                                                                                                              |  |  |

| BATDRV        | 21     | Ο   | P-channel battery FET (BATFET) gate driver output. It is shorted to VSYS to turn off the BATFET. It goes 10 V below VSYS to fully turn on BATFET. BATFET is in linear mode to regulate VSYS at minimum system voltage when battery is depleted. BATFET is fully on during fast charge and supplement mode.                                                                                 |  |  |

| BTST1         | 30     | PWR | Buck mode high side power MOSFET driver power supply. Connect a 0.047-µF capacitor between SW1 and BTST1. The bootstrap diode between REGN and BTST1 is integrated.                                                                                                                                                                                                                        |  |  |

| BTST2         | 25     | PWR | Boost mode high side power MOSFET driver power supply. Connect a $0.047$ - $\mu$ F capacitor between SW2 and BTST2. The bootstrap diode between REGN and BTST2 is integrated.                                                                                                                                                                                                              |  |  |

| CELL_BATPRESZ | 18     | I   | Battery cell selection pin for 1–4 cell battery setting. CELL_BATPRESZ pin is biased fro<br>VDDA. CELL_BATPRESZ pin also sets SYSOVP threshold to 5 V for 1-cell, 12 V for 2-<br>and 18.5 V for 3-cell. CELL_BATPRESZ pin is pulled below V <sub>CELL_BATPRESZ_FALL</sub> to ind<br>battery removal. The device exits LEARN mode, and disables charge. REG0x05/04() gi<br>back to default. |  |  |

## Pin Functions (continued)

| PIN      |        |     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |

|----------|--------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME     | NUMBER | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

| CHRG_OK  | 4      | 0   | Open drain active high indicator to inform the system good power source is connected to the charger input. Connect to the pullup rail via 10-k $\Omega$ resistor. When VBUS rises above 3.5V or falls below 24.5V, CHRG_OK is HIGH after 50ms deglitch time. When VBUS is falls below 3.2 V or rises above 26 V, CHRG_OK is LOW.                                                                                                                                                                                                                   |  |  |

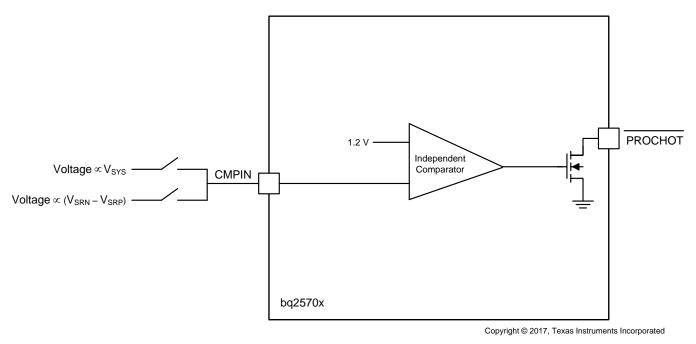

| CMPIN    | 14     | I   | Input of independent comparator. The independent comparator compares the voltage sensed<br>on CMPIN pin to internal reference, and its output is on CMPOUT pin. Internal reference,<br>output polarity and deglitch time is selectable by I2C. With polarity HIGH (REG0x30[6] = 1),<br>place a resistor between CMPIN and CMPOUT to program hysteresis. With polarity LOW<br>(REG0x30[6] = 0), the internal hysteresis is 100 mV. If the independent comparator is not in<br>use, tie CMPIN to ground.                                             |  |  |

| CMPOUT   | 15     | Ι   | Open-drain output of independent comparator. Place pullup resistor from CMPOUT to pullup supply rail. Internal reference, output polarity and deglitch time are selectable by I2C.                                                                                                                                                                                                                                                                                                                                                                 |  |  |

| COMP2    | 17     | Ι   | Buck boost converter compensation pin 2. Refer to bq25700 EVM schematic for COMP2 pin RC network.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| COMP1    | 16     | Ι   | Buck boost converter compensation pin 1. Refer to bq25700 EVM schematic for COMP1 pin RC network.                                                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| EN_OTG   | 5      | Ι   | Active HIGH to enable OTG mode. When EN_OTG pin is HIGH and REG0x35[4] is HIGH, OTG can be enabled, refer to USB On-The-Go (OTG) for details of how to enable OTG function                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| HIDRV1   | 31     | 0   | Buck mode high side power MOSFET (Q1) driver. Connect to high side n-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| HIDRV2   | 24     | 0   | Boost mode high side power MOSFET(Q4) driver. Connect to high side n-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| IADPT    | 8      | ο   | Buffered adapter current output. $V_{(IADP)} = 20 \text{ or } 40 \times (V_{(ACP)} - V_{(ACN)})$ . With ratio selectable in REG0x00[4]. Place a resistor from the IADPT pin to ground corresponding to inductor in use For 2.2 µH, the resistor is 137 k $\Omega$ . Place 100-pF or less ceramic decoupling capacitor from IADPT pin to ground. IADPT output voltage is clamped below 3.3 V.                                                                                                                                                       |  |  |

| IBAT     | 9      | 0   | Buffered battery current selected by I2C. $V_{(IBAT)} = 8 \text{ or } 16 \times (V_{(SRP)} - V_{(SRN)})$ for charge current, or $V_{(IBAT)} = 8 \text{ or } 16 \times (V_{(SRN)} - V_{(SRP)})$ for discharge current, with ratio selectable in REG0x00[3]. Place 100-pF or less ceramic decoupling capacitor from IBAT pin to ground. This pin can be floating if not in use. Its output voltage is clamped below 3.3 V.                                                                                                                           |  |  |

| ILIM_HIZ | 6      | I   | Input current limit input. Program ILIM_HIZ voltage by connecting a resistor divider from supply rail to ILIM_HIZ pin to ground. The pin voltage is calculated as: $V_{(ILIM_HIZ)} = 1 V + 40 \times IDPM \times RAC$ , in which IDPM is the target input current. The input current limit used by the charger is the lower setting of ILIM_HIZ pin and REG0x0F() and REG0x0E(). When the pin voltage is below 0.4 V, the device enters Hi-Z mode with low quiescent current. When the pin voltage is above 0.8 V, the device is out of Hi-Z mode. |  |  |

| LODRV1   | 29     | 0   | Buck mode low side power MOSFET (Q2) driver. Connect to low side n-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

| LODRV2   | 26     | 0   | Boost mode low side power MOSFET (Q3) driver. Connect to low side n-channel MOSFET gate.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

| PGND     | 27     | GND | Device power ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| PROCHOT  | 11     | 0   | Active low open drain output of processor hot indicator. It monitors ad <u>apter input</u> current, battery discharge current, and system voltage. After any event in the PROCHOT profile is triggered, a minimum 10-ms pulse is asserted. The pulse width is adjustable in REG0x36[5:2].                                                                                                                                                                                                                                                          |  |  |

| PSYS     | 10     | 0   | Current mode system power monitor. The output current is proportional to the total power from the adapter and battery. The gain is selectable through I2C. Place resistor from PSYS to ground to generate output voltage. This pin can be floating if not in use. Its output voltage is clamped below 3.3 V. Place a capacitor in parallel with resistor for filtering.                                                                                                                                                                            |  |  |

| REGN     | 28     | PWR | 6-V linear regulator output supplied from VBUS or VSYS. The LDO is active when VBUS above V <sub>VBUS_CONVEN</sub> . Connect a 2.2- or 3.3-μF ceramic capacitor from REGN to power ground. REGN pin output is for power stage gate drive.                                                                                                                                                                                                                                                                                                          |  |  |

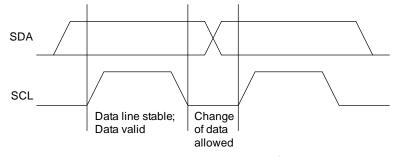

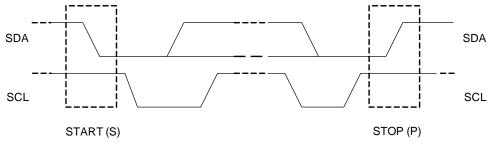

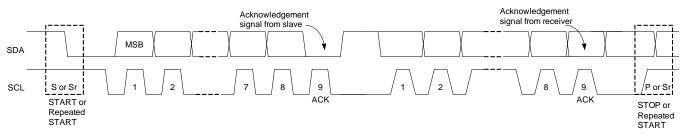

| SCL      | 13     | Ι   | I2C clock input. Connect to clock line from the host controller or smart battery. Connect a 10- $k\Omega$ pullup resistor according to I2C specifications.                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| SDA      | 12     | I/O | I2C open-drain data I/O. Connect to data line from the host controller or smart battery. Connect a $10$ -k $\Omega$ pullup resistor according to I2C specifications.                                                                                                                                                                                                                                                                                                                                                                               |  |  |

TEXAS INSTRUMENTS

www.ti.com

## Pin Functions (continued)

| PIN         |        | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|-------------|--------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME        | NUMBER | 1/0 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

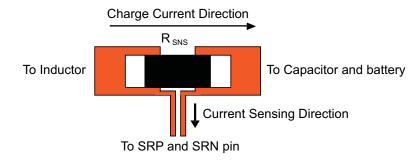

| SRN         | 19     | PWR | Charge current sense resistor negative input. SRN pin is for battery voltage sensing as well.<br>Connect SRN pin with optional $0.1$ - $\mu$ F ceramic capacitor to GND for common-mode filtering.<br>Connect a $0.1$ - $\mu$ F ceramic capacitor from SRP to SRN to provide differential mode filtering.<br>The leakage current on SRP and SRN are matched. For reverse battery plug-in protection,<br>$10$ - $\Omega$ series resistors are placed on SRP and SRN. |  |  |

| SRP         | 20     | PWR | harge current sense resistor positive input. Connect $0.1$ - $\mu$ F ceramic capacitor from SRP to RN to provide differential mode filtering. The leakage current on SRP and SRN are atched. For reverse battery plug-in protection, $10$ - $\Omega$ series resistors are placed on SRP and RN. Connect SRP pin with optional 0.1- $\mu$ F ceramic capacitor to GND for common-mode tering.                                                                         |  |  |

| SW1         | 32     | PWR | Buck mode high side power MOSFET driver source. Connect to the source of the high side<br>n-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                         |  |  |

| SW2         | 23     | PWR | Boost mode high side power MOSFET driver source. Connect to the source of the high side n-channel MOSFET.                                                                                                                                                                                                                                                                                                                                                           |  |  |

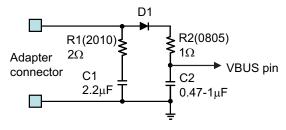

| VBUS        | 1      | PWR | Charger input voltage. An input low pass filter of $1\Omega$ and 0.47 $\mu$ F (minimum) is recommended.                                                                                                                                                                                                                                                                                                                                                             |  |  |

| VDDA        | 7      | PWR | nternal reference bias pin. Connect a 10- $\Omega$ resistor from REGN to VDDA and a 1- $\mu$ F eramic capacitor from VDDA to power ground.                                                                                                                                                                                                                                                                                                                          |  |  |

| VSYS        | 22     | PWR | Charger system voltage sensing. The system voltage regulation limit is programmed in REG0x05/04() and REG0X0D/0C().                                                                                                                                                                                                                                                                                                                                                 |  |  |

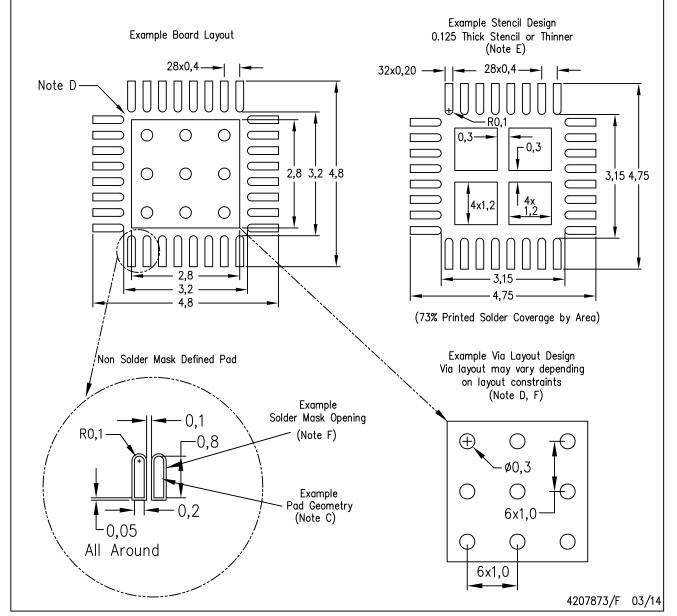

| Thermal pad | _      | _   | Exposed pad beneath the IC. Analog ground and power ground star-connected near the IC's ground. Always solder thermal pad to the board, and have vias on the thermal pad plane connecting to power ground planes. It also serves as a thermal pad to dissipate the heat.                                                                                                                                                                                            |  |  |

## 7 Specifications

## 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)(2)</sup>

|                                       |                                                                                                                   | MIN  | MAX | UNIT |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------|------|-----|------|

|                                       | SRN, SRP, ACN, ACP, VBUS, VSYS, BATDRV                                                                            | -0.3 | 30  |      |

|                                       | SW1, SW2                                                                                                          | -2.0 | 30  |      |

|                                       | BTST1, BTST2, HIDRV1, HIDRV2                                                                                      | -0.3 | 36  |      |

|                                       | LODRV1, LODRV2 (2% duty cycle)                                                                                    | -4.0 | 7   |      |

|                                       | HIDRV1, HIDRV2 (2% duty cycle)                                                                                    | -4.0 | 36  |      |

| Voltage                               | SW1, SW2 (2% duty cycle)                                                                                          | -4.0 | 30  | V    |

|                                       | SDA, SCL, REGN, CHRG_OK, CELL_BATPRESZ,<br>ILIM_HIZ, LODRV1, LODRV2, VDDA, COMP1, COMP2,<br>CMPIN, CMPOUT, EN_OTG | -0.3 | 7   |      |

|                                       | PROCHOT                                                                                                           | -0.3 | 5.5 |      |

|                                       | IADPT, IBAT, PSYS                                                                                                 | -0.3 | 3.6 |      |

| Differential values                   | BTST1-SW1, BTST2-SW2, HIDRV1-SW1, HIDRV2-SW2                                                                      | -0.3 | 7   | V    |

| Differential voltage                  | SRP-SRN, ACP-ACN                                                                                                  | -0.5 | 0.5 | V    |

| Junction temperature range, $T_J$     | Junction temperature range, T <sub>J</sub>                                                                        |      | 155 | °C   |

| Storage temperature, T <sub>stg</sub> |                                                                                                                   | -40  | 155 | °C   |

(1) Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) All voltages are with respect to GND if not specified. Currents are positive into, negative out of the specified terminal. Consult Packaging Section of the data book for thermal limitations and considerations of packages.

## 7.2 ESD Ratings

|     |                                             |                                                                                |       | VALUE | UNIT |

|-----|---------------------------------------------|--------------------------------------------------------------------------------|-------|-------|------|

| v   | V <sub>(Fob</sub> ) Electrostatic discharde | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 <sup>(1)</sup>              | ±2000 | V     |      |

| V(E |                                             | Charged-device model (CDM), per JEDEC specification JESD22-C101 <sup>(2)</sup> | ±500  | v     |      |

(1) JEDEC document JEP155 states that 500-V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250-V CDM allows safe manufacturing with a standard ESD control process.

## 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                |                                                                                                     | MIN   | MAX  | UNIT |  |

|----------------|-----------------------------------------------------------------------------------------------------|-------|------|------|--|

|                | ACN, ACP, VBUS                                                                                      | 0     | 24   |      |  |

|                | SRN, SRP, VSYS, BATDRV                                                                              | 0     | 19.2 |      |  |

|                | SW1, SW2                                                                                            | -2    | 24   |      |  |

| Voltage        | BTST1, BTST2, HIDRV1, HIDRV2                                                                        | 0     | 30   | V    |  |

| Vollage        | SDA, SCL, REGN, CHRG_OK, CELL_BATPRESZ, ILIM_HIZ, LODRV1, LODRV2, VDDA, COMP1, COMP2, CMPIN, CMPOUT | 0     | 6.5  | ·    |  |

|                | PROCHOT                                                                                             | 0     | 5.3  |      |  |

|                | IADPT, IBAT, PSYS                                                                                   | 0     | 3.3  |      |  |

| Differential   | BTST1-SW1, BTST2-SW2, HIDRV1-SW1, HIDRV2-SW2                                                        | 0     | 6.5  | N/   |  |

| voltage        | SRP-SRN, ACP-ACN                                                                                    | -0.35 | 0.35 | v    |  |

| Junction temp  | Junction temperature, T <sub>J</sub>                                                                |       | 125  | °C   |  |

| Operating free | -air temperature, T <sub>A</sub>                                                                    | -40   | 85   | °C   |  |

## 7.4 Thermal Information

|                       |                                              | bq25703A   |      |

|-----------------------|----------------------------------------------|------------|------|

|                       | THERMAL METRIC <sup>(1)</sup>                | RSN (WQFN) | UNIT |

|                       |                                              | 32 PINS    |      |

| $R_{\thetaJA}$        | Junction-to-ambient thermal resistance       | 37.2       | °C/W |

| R <sub>0JC(top)</sub> | Junction-to-case (top) thermal resistance    | 26.1       | °C/W |

| $R_{\theta J B}$      | Junction-to-board thermal resistance         | 7.8        | °C/W |

| ΨJT                   | Junction-to-top characterization parameter   | 0.3        | °C/W |

| ΨЈВ                   | Junction-to-board characterization parameter | 7.8        | °C/W |

| R <sub>0JC(bot)</sub> | Junction-to-case (bottom) thermal resistance | 2.3        | °C/W |

(1) For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

## 7.5 Electrical Characteristics

|                                                                                                                                         | PARAMETER                                                                           | TEST CONDITIONS        | MIN   | TYP                       | MAX                                                                                                                                                                                                                                                                                                                     | UNIT |

|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|------------------------|-------|---------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| V <sub>INPUT_OP</sub>                                                                                                                   | Input voltage operating range                                                       |                        | 3.5   |                           | 26                                                                                                                                                                                                                                                                                                                      | V    |

| REGULATION ACC                                                                                                                          | CURACY                                                                              |                        |       |                           |                                                                                                                                                                                                                                                                                                                         |      |

| MAX SYSTEM VOI                                                                                                                          | LTAGE REGULATION                                                                    |                        |       |                           |                                                                                                                                                                                                                                                                                                                         |      |

| V <sub>SYSMAX_RNG</sub>                                                                                                                 | System voltage regulation,<br>measured on V <sub>SYS</sub>                          |                        | 1.024 |                           | 19.2                                                                                                                                                                                                                                                                                                                    | V    |

|                                                                                                                                         |                                                                                     | REG0x05/04() = 0x41A0H |       | V <sub>SRN</sub> + 160 mV |                                                                                                                                                                                                                                                                                                                         | V    |

|                                                                                                                                         |                                                                                     | (16.800 V)             | -2%   |                           | 2%                                                                                                                                                                                                                                                                                                                      |      |

|                                                                                                                                         |                                                                                     | REG0x05/04() = 0x3130H |       | V <sub>SRN</sub> + 160 mV |                                                                                                                                                                                                                                                                                                                         | V    |

|                                                                                                                                         | System voltage regulation                                                           | (12.592 V)             | -2%   |                           | 2%                                                                                                                                                                                                                                                                                                                      |      |

| VSYSMAX_ACC                                                                                                                             | accuracy (charge disable)                                                           | REG0x05/04() = 0x20D0H |       | V <sub>SRN</sub> + 160 mV |                                                                                                                                                                                                                                                                                                                         | V    |

|                                                                                                                                         |                                                                                     | (8.400 V)              | -3%   |                           | 3%                                                                                                                                                                                                                                                                                                                      |      |

|                                                                                                                                         |                                                                                     | REG0x05/04() = 0x1060H |       | V <sub>SRN</sub> + 160 mV | 26         19.2         V         2%         V         3%         V         3%         V         3%         19.2         8         2%         4         3%         4         19.2         8         2%         4         3%         4         19.2         8         0.5%         2         0.5%         4         0.6% | V    |

|                                                                                                                                         | UT_OP         Input voltage operating range         3.5           SULATION ACCURACY | 3%                     |       |                           |                                                                                                                                                                                                                                                                                                                         |      |

| MINIMUM SYSTEM                                                                                                                          | I VOLTAGE REGULATION                                                                |                        |       |                           | I                                                                                                                                                                                                                                                                                                                       |      |

| V <sub>SYSMIN_RNG</sub>                                                                                                                 |                                                                                     |                        | 1.024 |                           | 19.2                                                                                                                                                                                                                                                                                                                    | V    |

|                                                                                                                                         |                                                                                     | REG0x0D/0C() = 0x3000H |       | 12.288                    |                                                                                                                                                                                                                                                                                                                         | V    |

|                                                                                                                                         |                                                                                     |                        | -2%   |                           | 2%                                                                                                                                                                                                                                                                                                                      |      |

|                                                                                                                                         | •••                                                                                 |                        |       | 9.216                     | mV 2%<br>mV 2%<br>mV 2%<br>mV 3%<br>mV 3%<br>mV 3%<br>288 2% 2<br>288 2% 2<br>216 2% 1<br>216 2% 1<br>384 4% 584 4%<br>584 4% 584 4% 584 4% 1<br>584 4% 584 4% 1<br>584 4% 584 4% 1                                                                                                                                     | V    |

|                                                                                                                                         |                                                                                     | REG0x0D/0C() = 0x2400H | -2%   |                           | 2%                                                                                                                                                                                                                                                                                                                      |      |

| V <sub>SYSMIN_REG_ACC</sub>                                                                                                             | enable, VBAT below                                                                  |                        |       | 6.144                     |                                                                                                                                                                                                                                                                                                                         | V    |

|                                                                                                                                         | REG0x0D/0C() setting)                                                               | REG0x0D/0C() = 0x1800H | -3%   |                           | 3%                                                                                                                                                                                                                                                                                                                      |      |

|                                                                                                                                         |                                                                                     |                        |       | 3.584                     |                                                                                                                                                                                                                                                                                                                         | V    |

| REGULATION ACCU<br>MAX SYSTEM VOLT<br>V <sub>SYSMAX_RNG</sub><br>V <sub>SYSMAX_ACC</sub><br>MINIMUM SYSTEM V<br>V <sub>SYSMIN_RNG</sub> |                                                                                     | REG0x0D/0C() = 0x0E00H | -3%   |                           | 4%                                                                                                                                                                                                                                                                                                                      |      |

| CHARGE VOLTAG                                                                                                                           | E REGULATION                                                                        |                        |       |                           |                                                                                                                                                                                                                                                                                                                         |      |

| V <sub>BAT RNG</sub>                                                                                                                    | Battery voltage regulation                                                          |                        | 1.024 |                           | 19.2                                                                                                                                                                                                                                                                                                                    | V    |

| 2,11,2,11,0                                                                                                                             |                                                                                     |                        |       | 16.8                      |                                                                                                                                                                                                                                                                                                                         | V    |

|                                                                                                                                         |                                                                                     | REG0x05/04() = 0x41A0H | -0.5% |                           | 0.5%                                                                                                                                                                                                                                                                                                                    |      |

|                                                                                                                                         |                                                                                     |                        |       | 12.592                    |                                                                                                                                                                                                                                                                                                                         | V    |

|                                                                                                                                         |                                                                                     | REG0x05/04() = 0x3130H | -0.5% |                           | 0.5%                                                                                                                                                                                                                                                                                                                    |      |

| V <sub>BAT_REG_ACC</sub>                                                                                                                |                                                                                     |                        | / •   | 8.4                       |                                                                                                                                                                                                                                                                                                                         | V    |

|                                                                                                                                         |                                                                                     | REG0x05/04() = 0x20D0H | -0.6% |                           | 0.6%                                                                                                                                                                                                                                                                                                                    |      |

|                                                                                                                                         |                                                                                     |                        | 0.075 | 4.192                     | 26<br>19.2<br>2%<br>2%<br>3%<br>3%<br>19.2<br>2%<br>2%<br>3%<br>4%<br>19.2<br>0.5%<br>0.5%<br>0.5%                                                                                                                                                                                                                      | V    |

|                                                                                                                                         |                                                                                     | REG0x05/04() = 0x1060H | 1 10/ |                           | 4 00/                                                                                                                                                                                                                                                                                                                   | •    |

## **Electrical Characteristics (continued)**

| P                  | PARAMETER                                                                                                                           | TEST CONDITIONS                               | MIN                                                                                                                                                                                                                                                                                                              | TYP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | MAX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | UNIT |

|--------------------|-------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| CHARGE CURRENT     | REGULATION IN FAST CHARG                                                                                                            | <b>BE</b>                                     |                                                                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

| Vireg_chg_rng      | Charge current regulation<br>differential voltage range                                                                             | VIREG_CHG = VSRP –<br>VSRN                    | 0                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 81.28                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | mV   |

|                    |                                                                                                                                     | REG0x03/02() = 0x1000H                        |                                                                                                                                                                                                                                                                                                                  | 4096                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | MAX         81.28         2%         3%         3%         3%         3%         3%         3%         3%         3%         3%         3%         3%         3%         3%         2%         3%         2%         3%         2%         2%         30%         10         25%         30%         10         4000         3000         1500         30%         10         44000         3000         1500         300         10         44200         3200         1700         700         1         19.52                                                                                                                                                                                                                                                           | mA   |

|                    |                                                                                                                                     | REG0003/02() = 0.000011                       | 0 $81.28$ $4096$ 2% $-3\%$ 2% $-4\%$ 3% $-4\%$ 3% $-1\%$ 1024 $-5\%$ 6% $-12\%$ 12% $-12\%$ 12% $-12\%$ 384 $2$ $384$ $-15\%$ $15\%$ $-25\%$ $25\%$ $-25\%$ $25\%$ $-20\%$ $20\%$ $-35\%$ $35\%$ $-25\%$ $25\%$ $-20\%$ $20\%$ $-35\%$ $35\%$ $-35\%$ $35\%$ $-30\%$ $30\%$ $-30\%$ $30\%$ $-12$ $10$ $-12$ $10$ |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |      |

|                    | Charge current regulation                                                                                                           | REG0x03/02() = 0x0800H                        |                                                                                                                                                                                                                                                                                                                  | 2048                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | mA   |

|                    | accuracy 10-m $\Omega$ current sensing resistor, VBAT above                                                                         |                                               | -4%                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

| CHRG_REG_ACC       | 0x0D/0C() setting (0°C to                                                                                                           | REG0x03/02() = 0x0400H                        |                                                                                                                                                                                                                                                                                                                  | 1024                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | mA   |

|                    | 85°C)                                                                                                                               |                                               | -5%                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 6%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |      |

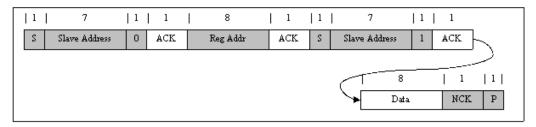

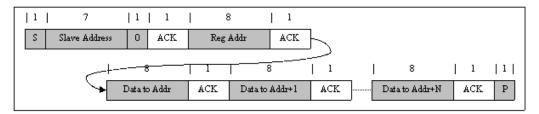

|                    |                                                                                                                                     | REG0x03/02() = 0x0200H                        |                                                                                                                                                                                                                                                                                                                  | 512                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 81.28         2%         3%         6%         12%         12%         25%         20%         35%         20%         35%         20%         35%         20%         35%         0         15%         20%         35%         0         10         4         4000         300%         10         4         4000         300%         10         700                                                                                                                                                                                                                                                                                                                                                                                                                    | mA   |