# Design guide IDP2303(A)

# Design guide for TV power supply with digital multi-mode PFC + LLC combo IC IDP2303(A)

## About this document

#### Scope and purpose

This design guide is to help customers design a TV power supply using an Infineon digital controller. It provides guidelines on power stage design, control parameters and protection settings as well as PCB layout and dpVision GUI usage.

#### Intended audience

This document is intended for design engineers that want to design a high performance TV power supply using Infineon's digital multi-mode PFC + LLC combo IC.

## Table of contents

| About this o | document                                                                     | 1    |

|--------------|------------------------------------------------------------------------------|------|

| Table of co  | ntents                                                                       | 1    |

| 1            | Abstract                                                                     | 3    |

| 2            | Introduction                                                                 | 4    |

| 2.1          | IC Introduction                                                              | 4    |

| 2.2          | Pin configuration and description                                            | 4    |

| 2.3          | Product highlights                                                           | 5    |

| 2.4          | Application                                                                  |      |

| 3            | PFC design                                                                   | 7    |

| 3.1          | Target specifications                                                        | 7    |

| 3.2          | Power stage                                                                  | 7    |

| 3.2.1        | Bridge rectifier                                                             | 7    |

| 3.2.2        | Selection of power MOSFET                                                    | 8    |

| 3.2.3        | MOSFET gate driving                                                          | 9    |

| 3.2.3.1      | Unique gate drive concept                                                    | 9    |

| 3.2.3.2      | Gate drive stability                                                         | 9    |

| 3.2.3.3      | Other design tips for the gate driving circuit                               | . 10 |

| 3.2.4        | Boost diode                                                                  | . 10 |

| 3.2.5        | Boost inductor                                                               | . 10 |

| 3.3          | Control parameters and protections                                           | . 12 |

| 3.3.1        | Output voltage sense and protections                                         | . 12 |

| 3.3.2        | Redundant OVP (ROVP)                                                         | . 13 |

| 3.3.3        | PFC ZCD divider design                                                       |      |

| 3.3.4        | Current sense and Over Current Protection (OCP)                              |      |

| 3.3.4.1      | Over Current Protection(OCP) tolerance & selection of current sense resistor |      |

| 3.3.4.2      | Verification of PFC inductance with OCP tolerance                            |      |

| 3.3.5        | Frequency law for multi-mode PFC                                             |      |

| 3.3.5.1      | Multimode PFC                                                                | . 19 |

| 3.3.5.2      | Frequency law                                                                | . 20 |

| 3.3.5.3      | Setting of <i>fmin</i> and <i>fmax</i>                                       | .21  |

| 3.3.6   | AC brown-in & out                                               | 22 |

|---------|-----------------------------------------------------------------|----|

| 4       | LLC design                                                      | 23 |

| 4.1     | Target specifications                                           | 23 |

| 4.2     | Power stage                                                     | 23 |

| 4.2.1   | System parameter calculation                                    | 23 |

| 4.2.2   | Main transformer and resonant network                           | 24 |

| 4.2.2.1 | Transformer turns ratio                                         | 24 |

| 4.2.2.2 | Equivalent circuit and resonant network                         | 25 |

| 4.2.2.3 | Calculation of transformer turn ratio                           | 27 |

| 4.2.2.4 | Selection of resonant factor m                                  |    |

| 4.2.2.5 | Selection of resonant capacitor                                 |    |

| 4.2.3   | Power MOSFET selection                                          | 29 |

| 4.2.4   | MOSFET gate driving                                             | 29 |

| 4.2.5   | Output rectifier                                                | 29 |

| 4.3     | Control parameters and protections                              |    |

| 4.3.1   | VCO frequency curve                                             |    |

| 4.3.1.1 | V_MinVCO and V_MaxVCO                                           | 31 |

| 4.3.1.2 | f_MinVCO and f_MaxVCO                                           | 31 |

| 4.3.1.3 | V_LLVCO : f_LLVCO (light load) : V_HLVCO : f_HLVCO (heavy load) | 32 |

| 4.3.2   | Current sense and OCP                                           | 32 |

| 4.3.3   | Dead time                                                       | 33 |

| 4.3.4   | LLC model and regulation loop                                   |    |

| 4.3.4.1 | LLC small signal model                                          | 33 |

| 4.3.4.2 | VCO modeling                                                    | 33 |

| 4.3.4.3 | LLC regulation loop                                             | 34 |

| 5       | General features and system design considerations               |    |

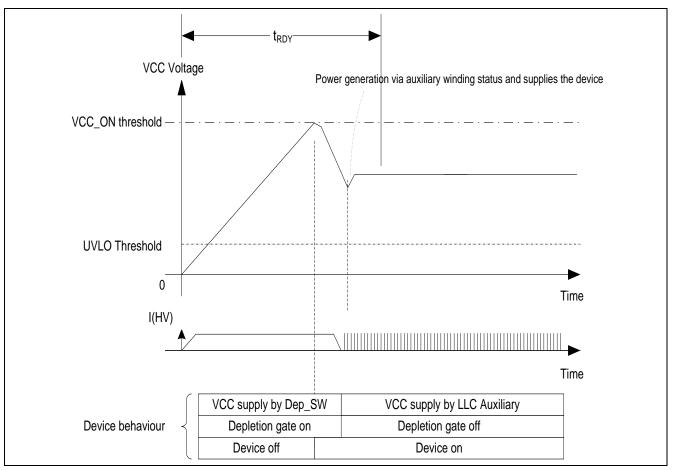

| 5.1     | VCC supply and high voltage startup cell                        |    |

| 5.1.1   | Start up                                                        |    |

| 5.1.2   | Selection of VCC capacitor                                      |    |

| 5.1.3   | VCC supply circuit linear regulator                             |    |

| 5.2     | LLC High-side VCC (HSVCC) cap                                   |    |

| 5.3     | Touch current                                                   |    |

| 5.4     | Black box                                                       | 38 |

| 6       | Tips on PCB layout                                              | 40 |

| 6.1     | Star connection of grounding                                    | 40 |

| 6.2     | Filtering capacitors                                            | 40 |

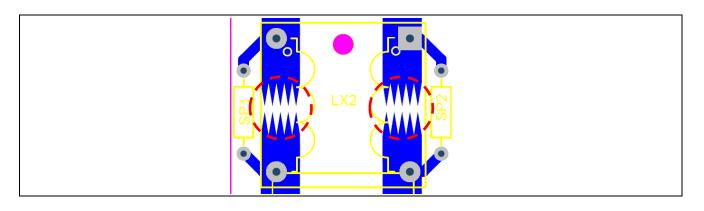

| 6.3     | PFC ZCD signal detection circuit                                | 41 |

| 6.4     | HBFB voltage detection circuit                                  | 41 |

| 6.5     | LLC high side bootstrap circuit                                 | 41 |

| 6.6     | Minimum current flowing loop area                               |    |

| 6.7     | Passing 4 kV lightning surge test                               | 42 |

| 6.8     | Other considerations                                            | 43 |

| 7       | Usage of dpVision                                               | 44 |

| 7.1     | Installation of dpVision                                        | 44 |

| 7.2     | Parameter setting with dpVision                                 | 46 |

| 8       | References                                                      | 49 |

# 1 Abstract

Infineon's digital platform controller IC (IDP2303(A)) combines the PFC and LLC controls for a high efficiency power supply. This design guide provides detailed calculation examples for major power stage component values as well as the settings for parameters associated with general functions and protection features. Useful tips on PCB layout are included to help the customers optimize their PCB design. Lastly, the installation and usage of a General User Interface - dpVision - is described to assist the customer in setting parameters for the digital IC.

The design example used in this guide is a 120 W power supply for a UHD TV. The customer can easily apply their own target specifications and obtain the design parameters by themselves.

# 2 Introduction

## 2.1 IC Introduction

The IDP2303(A) is a multi-mode PFC and LLC controller combined with a floating high side driver and a startup cell. A digital engine provides advanced algorithms for multi-mode operation to support the highest efficiency over the whole load range. A comprehensive and configurable protection feature set is implemented. Only a minimum of external components are required. The integrated HV startup cell and advanced burst mode enable the achievement of low stand-by power. In addition, a one-time-programming (OTP) unit is integrated to provide a wide set of configurable parameters that help to ease the design in phase of the project. [1][2].

## 2.2 Pin configuration and description

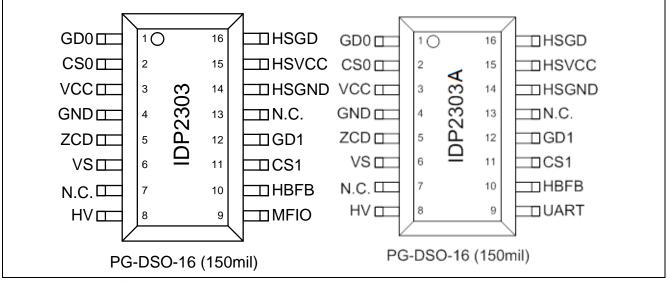

The pin configuration is shown in Figure 1 and Table 1.

Figure 1 Pin configuration

| Symbol  | Pin | Туре | Function                                                                                                                                           |

|---------|-----|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| GD0     | 1   | 0    | Gate driver output 0 (PFC gate driver)                                                                                                             |

| (PFCGD) |     |      | Output for directly driving the PFC PowerMOS. The default peak source current capability is 156 mA and the peak sink current capability is 800 mA. |

| CS0     | 2   | I    | Current sense 0 (PFC current sense)                                                                                                                |

| (PFCCS) |     |      | Pin CS0 is connected to an external shunt resistor and the source of the PFC                                                                       |

| (11000) |     |      | PowerMOS.                                                                                                                                          |

| VCC     | 3   | Р    | Positive voltage supply                                                                                                                            |

|         |     |      | IC power supply                                                                                                                                    |

| GND     | 4   | G    | Ground                                                                                                                                             |

|         |     |      | IC ground                                                                                                                                          |

| ZCD     | 5   | I    | Zero crossing detection                                                                                                                            |

|         |     |      | Pin ZCD is connected to the auxiliary winding of the PFC choke.                                                                                    |

Design guide IDP2303(A)

Т

| Introd | uction |

|--------|--------|

| intiou | uction |

Т

| Symbol     | Pin | Туре | Function                                                                                                                                                      |

|------------|-----|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VS         | 6   | 1    | Voltage sensing                                                                                                                                               |

|            |     |      | Pin VS is connected to a high ohmic resistor divider for directly sensing the bus                                                                             |

|            |     |      | voltage.                                                                                                                                                      |

| N.C.       | 7   | —    | Creepage distance                                                                                                                                             |

| HV         | 8   | 1    | High voltage input                                                                                                                                            |

|            |     |      | Pin HV is connected to the AC input via an external resistor and 2 diodes. There is                                                                           |

|            |     |      | a 600 V HV startup-cell internally connected that is used for initial VCC charge. It                                                                          |

|            |     |      | is also used to discharge the x-capacitors of the EMI network. Furthermore                                                                                    |

|            |     |      | sampled high voltage sensing is supported for brownin/brownout detection.                                                                                     |

| MFIO       | 9   | I    | MFIO                                                                                                                                                          |

| (UART for  |     |      | Pin MFIO provides a half duplex UART communication IO interface for parameter                                                                                 |

| IDP2303A)  |     |      | configuration. It also can be used for PFC output redundant over voltage                                                                                      |

|            |     |      | protection.                                                                                                                                                   |

|            |     |      |                                                                                                                                                               |

|            |     |      | Pin UART provides a half duplex UART communication IO interface for parameter                                                                                 |

|            |     |      | configuration and AC voltage detection.                                                                                                                       |

| HBFB       | 10  | 1    | Half bridge feedback                                                                                                                                          |

|            |     |      | Pin HBFB is connected to an optocoupler for the feedback path to control the                                                                                  |

|            |     |      | LLC switching frequency.                                                                                                                                      |

| CS1        | 11  | 1    | Current sense 1 (half bridge current sense)                                                                                                                   |

| (HBCS)     |     |      | Pin CS1 is connected to an external shunt resistor and the source of the                                                                                      |

| <u>CD1</u> | 12  | 0    | PowerMOS in the half-bridge stage.                                                                                                                            |

| GD1        | 12  | 0    | Gate driver output 1 (half bridge low side gate driver)                                                                                                       |

| (LSGD)     |     |      | Output for directly driving the lowside PowerMOS in the half-bridge. The peak source current capability is 120 mA and the peak sink current capability is 500 |

|            |     |      | mA.                                                                                                                                                           |

| N.C.       | 13  |      | Creepage distance                                                                                                                                             |

| HSGND      | 13  | G    | High side ground                                                                                                                                              |

| HIJGIND    | 14  | 0    | Ground for floating high side driver                                                                                                                          |

| HSVCC      | 15  | Р    | High side VCC                                                                                                                                                 |

|            | 10  |      | Power supply of the high side floating driver, supplied via bootstrap                                                                                         |

| HSGD       | 16  | 0    | High side floating gate driver                                                                                                                                |

|            |     | -    | Output for directly driving the high side PowerMOS in the half-bridge. The peak                                                                               |

|            |     |      | source current capability is 0.52 A and the peak sink current capability is 1.3 A.                                                                            |

|            | 1   |      |                                                                                                                                                               |

## 2.3 Product highlights

- Integrated 600 V startup cell

- Integrated floating driver based on coreless transformer technology

- Digital multi-mode operation for higher efficiency

- Supports low standby power by means of a direct X-cap discharge function and advanced burst mode control

- Eliminates the auxiliary power supply by means of an integrated startup cell and burst mode

- UART interface for communication and in-circuit configuration

- Flexible design-in by means of one time programming capability for a wide range of parameters

# 2.4 Application

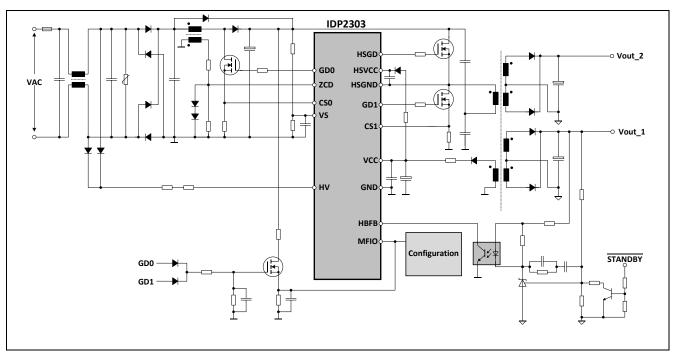

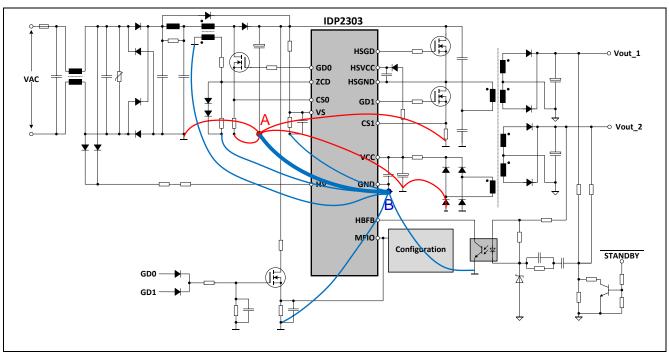

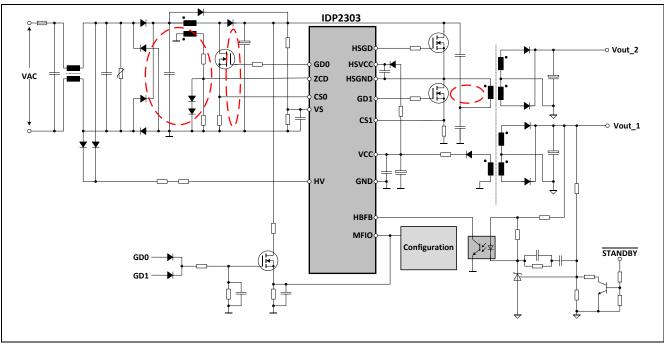

Figure 2 Typical application circuit for a power supply with IDP2303

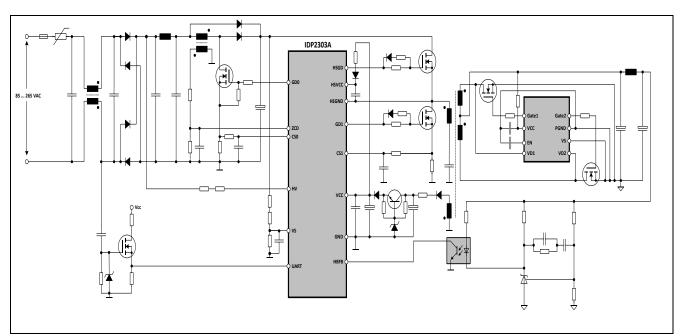

Figure 3 Typical application circuit for a power supply with IDP2303A

# 3 PFC design

## 3.1 Target specifications

Table 2 shows the major specifications for the target PFC design.

#### Table 2System specification

| Parameter                                               | Symbol                      | Value | Unit            |

|---------------------------------------------------------|-----------------------------|-------|-----------------|

| Input voltage minimum                                   | V <sub>in_min</sub>         | 90    | $V_{\text{AC}}$ |

| Input voltage maximum                                   | V <sub>in_max</sub>         | 265   | $V_{\text{AC}}$ |

| Nominal bus voltage                                     | V <sub>bus</sub>            | 390   | V               |

| PFC output power                                        | $P_{o_PFC}$                 | 130   | W               |

| Estimated efficiency of system (PFC+LLC) at 90 $V_{AC}$ | Ŋ <sub>sys</sub>            | > 87% |                 |

| Estimated efficiency of PFC at 90 V <sub>AC</sub>       | η <sub>ρες</sub>            | ~93%  |                 |

| Estimated efficiency of PFC at 265 V <sub>AC</sub>      | <b>η</b> <sub>PFC_265</sub> | ~96%  |                 |

| Minimum switching frequency                             | f <sub>sw_min</sub>         | 25    | kHz             |

| Power factor                                            |                             | > 0.9 |                 |

#### 3.2 Power stage

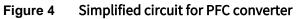

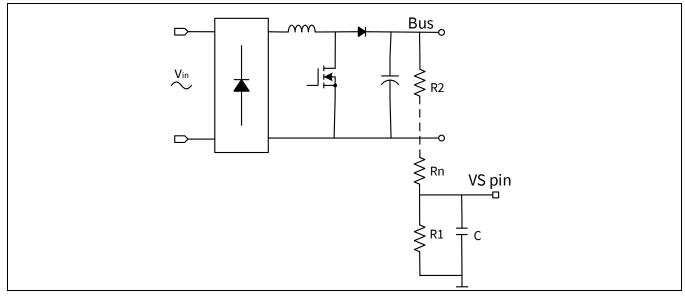

A simplified application circuit for PFC stage is given in Figure 4.

## 3.2.1 Bridge rectifier

The total bridge power loss is calculated using the average input current flowing through two of the bridge rectifying diodes.

$$P_{rect\_loss} = I_f * 2V_f = \frac{2\sqrt{2}}{\pi} \frac{P_o}{V_{in\_min} * \eta_{PFC_{90}}} * 2V_f = \frac{4\sqrt{2}}{\pi} \frac{130}{90 * 0.93} * 2 * 0.35 = 1.96 W$$

Knowing the value of the power loss, one can choose an appropriate bridge rectifier based on its thermal characteristics.

## 3.2.2 Selection of power MOSFET

In order to select an optimum MOSFET, one must understand the MOSFET requirements in a DCM boost converter [3]. The following are some major MOSFET selection considerations:

- Low Figure of Merit  $R_{on}{}^{\star}Q_{g}$  and  $R_{on}{}^{\star}Q_{oss}$

- Fast Turn-on/off switching to reduce the device switching losses

- Low output capacitance C<sub>oss</sub> for low switching energy, to increase light load efficiency.

- Switching and conduction losses must be balanced for minimum total loss this is typically optimized at the low line condition, where worst case losses and temperature rises occur.

- V<sub>DS</sub> rating to handle spikes/overshoots

- Low thermal resistance R<sub>thJC</sub>. Package selection must consider the resulting total thermal resistance from junction to ambient.

- Body diode speed and reverse recovery charge are not important, since the body diode never conducts in a boost converter.

Infineon high voltage MOSFETs have several families based on different technologies, each of which target a specific application, topology or operation. Several CoolMOS<sup>™</sup> series devices can be used for boost applications depending upon the customer's requirement for the voltage rating and thermal characteristics.

With the CE in 500 V, E6 and P6 family in 600 V, Infineon offers various series with extremely low conduction and switching losses that can make switching applications more efficient, more compact, lighter and cooler.

Two IPD50R280CE in parallel are preselected for the design and their parameters will be used for the loss calculation. The thermal characteristic can be estimated and the device shall be replaced if it cannot meet the thermal requirement at the end of the calculation process.

The conduction loss dissipated by each MOSFET is calculated as:

$$P_{con} = \left(\frac{I_{Q_{rms}}}{2}\right)^2 R_{DS_{on}} = \left(\frac{1.5}{2}\right)^2 * 0.5 = 0.28 W$$

In which,

$$I_{Q\_rms} = I_{peak\_Vin\_min} \sqrt{\frac{1}{6} - \frac{4\sqrt{2}V_{in\_min}}{9\pi V_{bus}}} = \frac{2\sqrt{2}P_{o\_PFC}}{\eta_{PFC\_90} * V_{in\_min}} \sqrt{\frac{1}{6} - \frac{4\sqrt{2}V_{in\_min}}{9\pi V_{bus}}} = \frac{2\sqrt{2} * 130}{0.93 * 90} \sqrt{\frac{1}{6} - \frac{4\sqrt{2} * 90}{9\pi * 390}} = 4.39 * 0.347 = 1.5 A$$

$R_{DS_{on}} = 0.5 \ \Omega$  is the on-state resistance of the MOSFET at a junction temperature of 100°C.

For CrCM or DCM operation, the turn-on loss due to the voltage-current crossover is negligible because when MOSFET turns on, the MOSFET current rises from zero. Therefore, only the loss due to the discharge of the drain-source capacitance of the MOSFET shall be considered.

The calculation of the MOSFET discharge loss at turn-on ( $P_{discharge}$ ) and turn-off loss ( $P_{turnoff}$ ) is complicated due to the changing values of voltage, current, frequency etc. over the whole AC cycle. So based on a rule-of-thumb, the total switching loss for each MOSFET is roughly estimated as half of the conduction loss.

$$P_{sw} = \frac{1}{2}P_{con} = 0.5 * 0.28 = 0.14 W$$

Then the total power loss of each MOSFET can be estimated as:

$$P_{MOS\_loss} = P_{con} + P_{sw} = 0.42 W$$

## 3.2.3 MOSFET gate driving

## 3.2.3.1 Unique gate drive concept

The IDP230x gate drive offers unique features including configurable charge current and output voltage, which offer many advantages (Figure 5):

- turn-on slope optimization for EMI by configurable current with dpVision

- no need to solder and re-solder resistors

- turn-off current limited by external R<sub>gate</sub>

- due to fast 1 A/0.5 A discharge, a local discharge PNP transistor is not required in some relatively low power applications

- V<sub>gate\_high</sub> up to VCC possible (rail-to-rail operation)

Figure 5 Gate drive concept

## 3.2.3.2 Gate drive stability

Due to the unique gate drive with configurable charge current and regulated gate high voltage,  $R_{gate}$  should not be too large. Table 3 shows the recommend range for stable gate drive operation. A 10 $\Omega$   $R_{gate}$  resistor is suitable for most applications. Soft turn-on for trouble-free EMI is guaranteed by the configurable constant current gate charging.

| Table 3 | Recommended R <sub>gate</sub> values fo | r different C <sub>gate</sub> , R <sub>g</sub> | and gate source current |

|---------|-----------------------------------------|------------------------------------------------|-------------------------|

|---------|-----------------------------------------|------------------------------------------------|-------------------------|

| C <sub>gate</sub> (nF)            | 1.0~2.0 |       |      |       |  |

|-----------------------------------|---------|-------|------|-------|--|

| Gate source current (mA)          | 100     |       | 310  |       |  |

| R <sub>gs</sub> (Ω)               | 10 k    | 100 k | 10 k | 100 k |  |

| Recommended R <sub>gate</sub> (Ω) | 5~20    | 15~25 | 4~14 | 2~18  |  |

## 3.2.3.3 Other design tips for the gate driving circuit

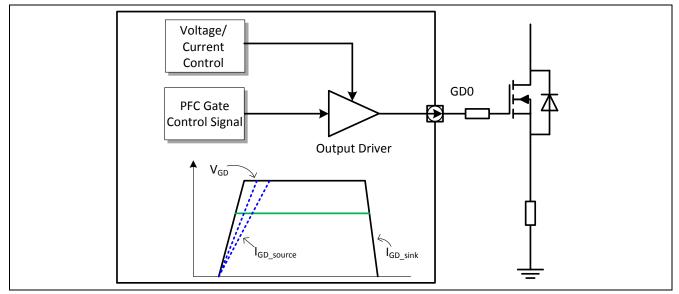

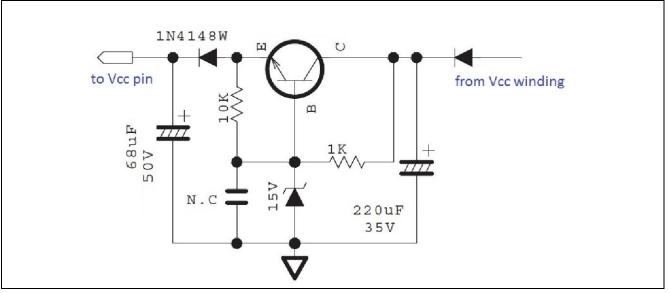

For some high power SMPS applications, two MOSFETs are often connected in parallel for the PFC converter. In this case, it is recommended to enhance the PFC driving capability by adding an additional circuit close to the PFC MOSFET, as shown in the example in Figure 6.

During turn-off, transistors Q3 and Q4 are turned on, discharging the PFC MOSFET gate capacitor. As a result, the turn-off of the MOSFETs is accelerated, which reduces the MOSFETs turn-off losses. Meanwhile, the turn-on is defined by the constant gate charge current, which can be kept relatively slow for better EMI performance.

Apart from the gate drive resistance itself,  $10 \text{ k}\Omega$  resistors (R5 and R6) are also commonly connected between MOSFET gate and source to help damping some overshoot and oscillations and discharge gate capacitor when there is no gate signal.

Figure 6 PFC gate driving circuit

## 3.2.4 Boost diode

To select an appropriate boost diode, its thermal characteristic needs to be considered. The average diode current can be calculated by:

$$I_{D_{avg}} = I_{o_{PFC}} = \frac{P_{o_{PFC}}}{V_{bus}} = \frac{130}{390} = 0.33 A$$

The total diode conduction loss can be calculated by:

$P_{D_{loss}} = I_{D_{avg}} * V_f = 0.33 * 0.5 = 0.17 W$

## 3.2.5 Boost inductor

One of the key design considerations for a boost inductor is to ensure the minimum switching frequency is always higher than 25 kHz to avoid any audible noise. The worst cases are usually at extremes of operation such as minimum and maximum voltage and during start up and load transients - e.g. twice full power.

## Design guide IDP2303(A) PFC design

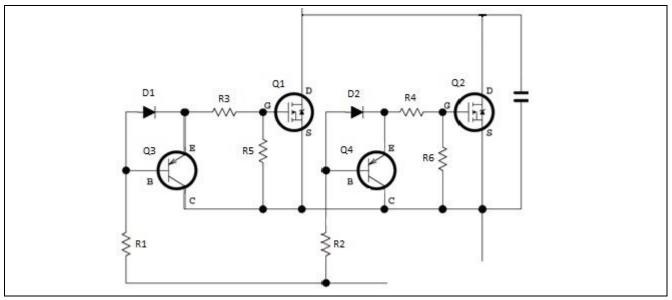

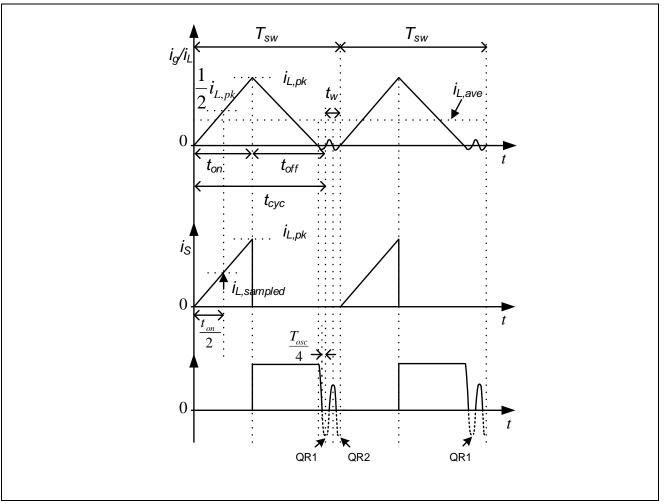

Figure 7 Current and timing in QR1 operation

With the IDP230x, the minimum switching frequency of 25 kHz is guaranteed by the "maximum switching period time-out" approach, which turns the MOSFET on when 40 us of switching period is reached. Based on the PFC control concept of the IDP230x, the frequency may reach the 25 kHz limit in two extreme conditions:

- Heavy load when QR=1 (MOSFET turn-on at the first switching valley according to the frequency law, which will be discussed in a later section of this document.)

- Light load when QRN>10 according to the frequency law, or when the ZCD signal is too weak to be detected within 40 us.

The second condition will not affect the design of inductor.

Figure 7 illustrates the inductor current and timing during QR1 operation. In which

$$T_{osc} = 2\pi \sqrt{L_{PFC}C_{oss}}$$

Where  $L_{PFC}$  is the PFC inductance and  $C_{oss}$  is the time related output capacitance of the PFC MOSFET.  $T_{osc}$  is usually around 1 us, and is negelected in the analysis below to simplify the calculation. The switching frequency at the AC peak, double full load with QR1 operation can be calculated as:

$$f = \frac{v_{in_{pk}}^{2} * (v_{bus} - v_{in_{pk}}) * \eta}{v_{bus} * L_{PFC} * 8P_{o_{pFC}}}$$

For 265  $V_{\text{ac}}$ ,

$$f_{265V_pk} = \frac{(265 * \sqrt{2})^2 * (390 - 265 * \sqrt{2}) * \eta_{PFC_265}}{390 * L_{PFC} * 8P_{o_PFC}} = \frac{658}{L_{PFC} * P_{o_PFC}}$$

For 90  $V_{ac}$ ,

$$f_{90V\_pk} = \frac{(90 * \sqrt{2})^2 * (390 - 90 * \sqrt{2}) * \eta_{PFC\_90}}{390 * L_{PFC} * 8P_{o\_PFC}} = \frac{1268}{L_{PFC} * P_{o\_PFC}}$$

Comparing the switching frequency at 265 Vac and 90 Vac peak, it is obvious that the frequency at 265 Vac is lower. Therefore,

$$f_{265V_pk} > 25 \ kHz$$

Then the PFC inductance to meet the requirement can be calculated as:

Application Note

#### Design guide IDP2303(A)

PFC design

$$L_{PFC} < \frac{v_{265\_pk}^2 * \left(v_{bus} - v_{265\_pk}\right) * \eta_{PFC\_265}}{v_{bus} * f * 8P_{o\_PFC}} = \frac{(265 * \sqrt{2})^2 * (390 - 265 * \sqrt{2}) * 0.96}{390 * 25 * 10^3 * 8 * 130} = 202 \, uH$$

Thereby, a PFC inductance of 200  $\mu$ H is selected.

Another design consideration for the boost inductor is to ensure that the ferrite core will not go into saturation. Then the number of turns in the winding is calculated as:

$$N_{PFC} > \frac{i_{pk_90Vac} * L_{PFC}}{B_{max}A_{min}} = \frac{4.33 * 200 * 10^{-6}}{0.3 * 99 * 10^{-6}} = 29$$

in which

$$i_{pk\_90Vac} = \frac{2\sqrt{2}P_{o\_PFC}}{\eta * v_{90}} = \frac{2\sqrt{2} * 120}{0.87 * 90} = 4.39A$$

$B_{max}$  is up to 0.3T,  $A_{min}$  is  $99mm^2$  if an EQ30 core with PC40 ferrite material is selected.

After the threshold of Over Current Protection (OCP) is defined and its tolerance taken into consideration, verification is needed that the inductor is able to carry the maximum current defined by OCP, and not become saturated. Otherwise, a large current will result from the saturation, and potentially damage devices if it is present for some time.

## 3.3 Control parameters and protections

#### 3.3.1 Output voltage sense and protections

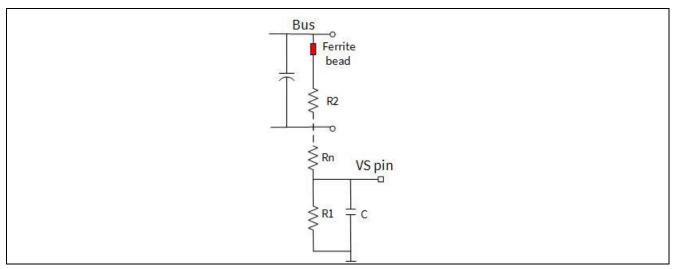

The VS pin is used for feedback regulation of the PFC Bus voltage. A simple resistor divider is used to step down the bus voltage as shown in Figure 8.

Figure 8 PFC bus voltage sensing

It is recommended to use sense resistors with a tolerance of 1% for accurate sensing. Due to the voltage stress across the upper arm resistor, it is recommended to split this value into a few resistors in series. In order to achieve a better standby performance, the resistance of sensing resistors is suggested to select a

high value. The power loss brought by these sensing resistors under standby operation can be calculated as:  $V_{c}$  <sup>2</sup>

$$P_{Rs\_loss} = \frac{V_{bus}^2}{R_1 + R_2 + \dots + R_n}$$

Application Note

To meet the low standby power consumption requirement, P<sub>Rs\_loss</sub> should be optimized. For example, the expected maximum power loss across these resistors, which occurs at 264Vac, is designed to be less than 15mW under standby operation,

$$P_{Rs\_loss} = \frac{\left(\sqrt{2}*264\right)^2}{R_1 + R_2 + \dots + R_n} < 15 mW.$$

So (R1+...+Rn) is calculated to be higher than 9.3 M $\Omega$ .

A capacitor of approximately 1nF should be added at the VS pin to ground to filter high frequency switching noise.

$$V_s = \frac{R_1}{R_1 + R_2 + \dots + R_n} V_{bus}$$

For Over Voltage Protection (OVP), if the average sensed PFC bus voltage exceeds the OVP threshold, the PFC will stop switching while the LLC continues to run. Once the average sensed PFC bus voltage reduces and reaches the reference bus voltage, the PFC converter resumes normal operation.

The PFC Under Voltage Protection (UVP) is a protection for the LLC converter against LLC input under voltage, to avoid LLC transformer saturation or capacitive mode operation. If the average sensed PFC bus voltage falls below a configurable UVP threshold for a blanking time, then PFC under voltage is detected. As a result, PFC and LLC will stop switching immediately.

## 3.3.2 Redundant OVP (ROVP)

Customers may request an additional protection, Redundant Overvoltage Protection (ROVP) in case there is a component failure in the main OVP voltage divider, for a higher level of reliability.

At the same time, the requirements for standby power consumption of a power supply unit (PSU) in TV applications becomes more and more stringent.

To implement ROVP, a voltage divider consisting of resistors is usually connected between the bus and ground to detect the bus voltage (usually 350 V in standby mode, and 390 V in normal mode). These resistors will consume some power (p=v^2/R, usually 30~100 mW), which adds to the total power consumption of the PSU, and becomes a critical concern in standby mode.

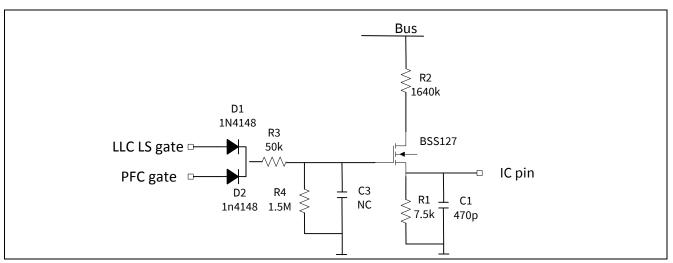

Figure 9 shows a typical ROVP circuit, which is almost lossless during standby mode.

Figure 9 Typical circuit of ROVP

In Figure 9, R1&R2 are the resistor voltage divider to detect the bus voltage. The voltage divider is effective only when the BSS127 MOSFET is turned on.

The BSS127 gate drive consists of:

- two small signal diodes D1 & D2 to introduce LLC and PFC gate signals as control inputs

- R3 as a current limiter at turn on

- R4 & C3 (the input capacitance of BSS127 or an additional capacitor) network, as an RC integrator that converts "pulse" signal into a "step" signal.

In standby mode, during burst-on, when there is either PFC or LLC switching, the BSS127 MOSFET will be turned on and the voltage divider is connected to the MCOM (Multi-function and Communication) pin to detect bus voltage. During burst-off, when there is neither PFC nor LLC gate switching, the BSS127 MOSFET is open and the voltage divider is out-of-circuit. Thus, the conduction loss in the voltage divider can be avoided during burst-off, thereby saving power during standby.

During normal operation when the load is usually much larger, the IC is always active and the PFC and/or LLC switch continuously so the voltage divider is always in-circuit. However, the conduction loss is only a very small portion of the total loss.

With the IDP2303, the MFIO pin is used for PFC output ROVP.

As the MCOM pin is a multifunction pin, that is not dedicated for high impedance bus voltage sensing, it **must not** be connect to the bus voltage divider at start up. Current leakage into the pin during system startup could affect the IC start-up behaviour. The proposed solution above with the BSS127 ensures a proper start-up and an almost lossless 2nd OVP function, which is almost lossless during standby mode.

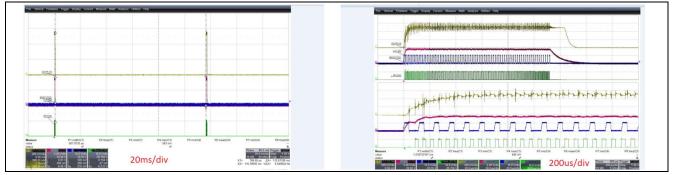

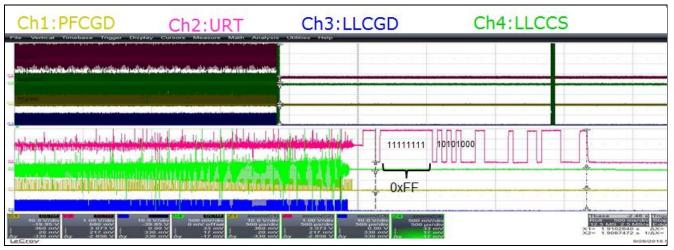

Below in Figure 10 are the typical waveforms of PFC (green) and LLC (blue) gate signals, the gate signal of BSS127 (red) and voltage at the MCOM pin (yellow).

Figure 10 Typical waveforms during standby(left:20 ms/div; right: 20 ms/div)

After the IC wakes from sleep mode, the firmware starts to check the voltage at the MCOM pin after it reaches a peak and is stable. If the ROVP threshold is reached, after a defined blanking time, the IC ceases PFC switching.

If the ROVP function is not needed, customers can connect a resistor between the MCOM and GND pins to pull the ROVP pin voltage below the threshold to disable ROVP.

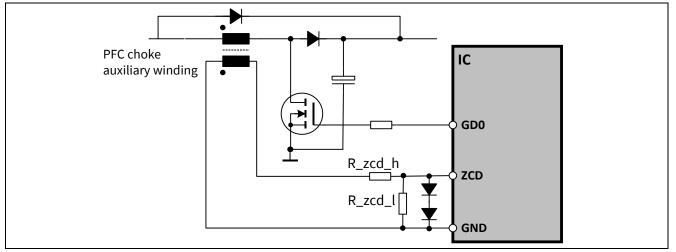

## 3.3.3 PFC ZCD divider design

To ensure apporiate operation of PFC ZCD detection, the value of R\_zcd\_h and R\_zcd\_l, as well as the PFC inductor turn ratio, should be optimized. For PFCZCD pin, there are an internal negative clamping ( $V_{INPCLN}$ ), as shown in Ttable 4, with current capabitly of 2.5mA and a positive clampling ( $V_{D_zcd}$ ) by two external diodes. Thus PFCZCD pin voltage can be calculated during PFC MOSFET on and inductor demagnetizing period.

$$\text{PFC MOSFET on: } V_{zcd} = \begin{cases} -\frac{VIN}{n} \frac{R_{zcd_{l}l}}{R_{zcd_{h}+R_{zcd_{l}l}}}, -\frac{VIN}{n} \frac{R_{zcd_{l}l}}{R_{zcd_{h}+R_{zcd_{l}l}}} > V_{INPCLN} \\ V_{INPCLN}, -\frac{VIN}{n} \frac{R_{zcd_{l}l}}{R_{zcd_{h}+R_{zcd_{l}l}}} \leq V_{INPCLN} \\ \end{cases}$$

$$\text{PFC inductor demagnetizing period: } V_{zcd} = \begin{cases} \frac{VBUS-VIN}{n} \frac{R_{zcd_{l}l}}{R_{zcd_{h}+R_{zcd_{l}l}}}, \frac{VBUS-VIN}{n} \frac{R_{zcd_{l}l}}{R_{zcd_{h}+R_{zcd_{l}l}}} \\ V_{D_{zcd}}, \frac{VBUS-VIN}{n} \frac{R_{zcd_{l}l}}{R_{zcd_{h}+R_{zcd_{l}l}}} \geq V_{D_{zcd}} \end{cases} \end{cases}$$

In order to get a better noise Immunization performance, PFCZCD voltage is recommended to be higher than the clamping voltage. Thus the clamping current can be calculated as:

Negative clamping current:  $I_{zcd} = -\frac{\left(\frac{VIN}{n} - V_{INPCLN}\right)}{R_{zcd}h}$ Positive clamping current:  $I_{zcd} = \frac{\left(\frac{V_{bus} - VIN}{n} - V_{D_{zcd}}\right)}{R_{zcd}h}$

For example, with a turn ratio of 8, diode forward voltage drop of 0.7V each, and minimum negative claming voltage 0.14V, the minimum resistor ratio can be calculated:

$$V_{zcd} = \frac{390 - \sqrt{2} * 264}{8} \frac{R_{zcd_l}}{R_{zcd_l} + R_{zcd_l}} > 1.4,$$

where we can get  $\frac{R_z c d_l}{R_z c d_h + R_z c d_l} > 0.67$ . Based on the maximum negative clamping current, we could have

$$I_{zcd} = -\frac{\left(\frac{VIN}{n} - 0.14\right)}{R_{zcd}h} > -2.5mA.$$

Thus,

$R_{zcd\_h} > 18.6k\Omega$

Based on the calculation, the R\_zcd\_h can select a resistor of higher than 18.6k, while R\_zcd\_l can be higher than 2 times of R\_zcd\_h.

#### Table 4PFCZCD Parameters

| Parameters                            | Symbol               |      | Values |      | Unit | Note/Test Condition      |

|---------------------------------------|----------------------|------|--------|------|------|--------------------------|

|                                       |                      | Min. | Тур.   | Max. |      |                          |

| Zero-crossing threshold               | VZCTHR               | 15   | 40     | 70   | mV   |                          |

| Comparator propagation delay          | t <sub>zcpd</sub>    | 30   | 50     | 70   | ns   | $dV_{ZCD}/dt = 4V/\mu s$ |

| Input voltage negative clamping level | -V <sub>INPCLN</sub> | 140  | 180    | 220  | mV   |                          |

## 3.3.4 Current sense and Over Current Protection (OCP)

The PFCCS pin is used to sense the drain-source current of the switching MOSFET. The voltage measured is only valid after a certain blanking time following the turn-on of the switch. A low pass RC filter should be added the pin to filter high frequency switching noise.

An appropriate sensing resistor value should ensure that:

- The triggering of OCP protects the PFC inductor from saturation and other components from over current stress.

- The triggering of OCP does not occur during normal operation.

# 3.3.4.1 Over Current Protection(OCP) tolerance & selection of current sense resistor

From the datasheet (Table 5), the parameters of the IC that will affect OCP protection tolerance are:

- OCP1 threshold tolerance

- OCP1 comparator propagation delay

Table 5

Electrical characteristics of the CSx pin

| Parameters                                                                                  | Symbol                   | Symbol Values |      |      |    | Note/Test condition                                                              |

|---------------------------------------------------------------------------------------------|--------------------------|---------------|------|------|----|----------------------------------------------------------------------------------|

|                                                                                             |                          | Min.          | Тур. | Max. |    |                                                                                  |

| OCP, OCP1 threshold tolerance                                                               | $\Delta V_{\text{OCP1}}$ | —             | —    | ±6.2 | %  |                                                                                  |

| Delay from V <sub>CSx</sub> crossing V <sub>CSxOCP1</sub><br>to CSx_OCP1 rising edge, 1.2 V | t <sub>csocp1</sub>      | 20            | 320  | 620  | ns | <sup>1</sup> input signal slope<br>dV <sub>cs</sub> /dt = 10 mV/μs <sup>2</sup>  |

|                                                                                             |                          | 90            | 170  | 250  | ns | <sup>1</sup> input signal slope<br>dV <sub>cs</sub> /dt = 150 mV/μs <sup>2</sup> |

| range                                                                                       |                          | 90            | 140  | 210  | ns | <sup>1</sup> input signal slope<br>dV <sub>cs</sub> /dt = 300 mV/μs <sup>2</sup> |

<sup>1</sup> Not tested in production test.

<sup>2</sup> This slope represents a use case of a switch-mode power supply with minimum input voltage.

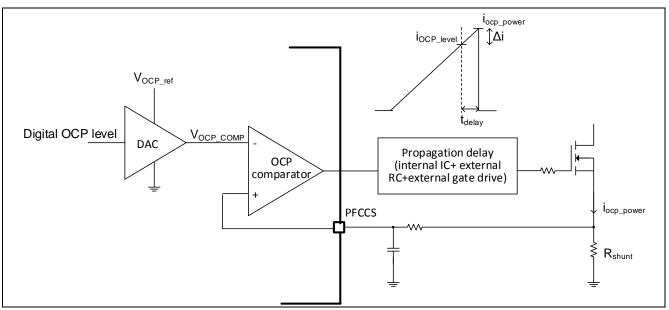

In reality, external circuit specifications also come into play. For example, from Figure 11, it can be seen that the external parameters affecting OCP protection are:

- The gain error caused by the external RC filter

- The external delay caused by the RC filter

- External propagation delays caused by the gate discharge and MOSFET drain-source capacitor discharge

Figure 11 OCP protection implementation structure

A spradsheet-based calculation example for selecting the current sense resistor and the OCP tolerance is shown in Figure 12.

|                                                   | tolerance     | unit   | min      | typ   | max      | note                                                                                                                                                             |

|---------------------------------------------------|---------------|--------|----------|-------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Calculation of OCP                                |               |        |          |       |          |                                                                                                                                                                  |

| OCP1 threshold                                    | 6.20%         | mV     | 563      | 600   | 637      |                                                                                                                                                                  |

|                                                   | 1%            | Ω      | 504.9    | 510   | 515.1    |                                                                                                                                                                  |

| R <sub>filter</sub><br>C <sub>filter</sub>        | 20%           | pF     | 800.0    | 1000  | 1200.0   | selected by customer                                                                                                                                             |

| fsw                                               | 2070          | kHz    | 60.0     | 90    | 1200.0   | Frequency law range                                                                                                                                              |

|                                                   |               | KTIZ   | 0.906    | 0.961 | 0.989    |                                                                                                                                                                  |

| RC filter gain <i>g<sub>filter</sub></i>          |               |        | 0.900    | 0.901 | 0.989    | $g_{filter} = \frac{1}{\sqrt{1 + (2\pi f RC)^2}}$                                                                                                                |

| OCP1 level after RC<br>filter gain                |               |        | 510      | 577   | 630      |                                                                                                                                                                  |

| OCP1 level tolerance<br>with RC filter            |               |        | -11.51%  | 577   | 9.27%    |                                                                                                                                                                  |

| Calculation of OCP de                             | elay time:    |        |          |       |          |                                                                                                                                                                  |

| delay caused by RC                                |               |        | 402.0    | 510   | 610.1    | 7-BC                                                                                                                                                             |

| filter $	au$                                      |               | ns     | 403.9    | 510   | 618.1    | $\tau = RC$                                                                                                                                                      |

| internal propagation                              |               |        | 222      |       | 12221    |                                                                                                                                                                  |

| delay t <sub>int</sub>                            |               | ns     | 90       | 170   | 250      | Internal Propagation delay                                                                                                                                       |

| external propagation<br>delay<br>t <sub>ext</sub> | 20%           | ns     | 200.0    | 250   | 300.0    | external Propagation delay from IC gate low<br>threshold to MOSFET off, including gate<br>discharge, MOSFET drain source cap discharge<br>(measured by customer) |

| Calculation of $\Delta I$ due                     |               |        |          |       |          |                                                                                                                                                                  |

| lowest V_in (results                              |               | -      | 1202020  | 23    | 12/2/12/ |                                                                                                                                                                  |

| in max. current)                                  |               | Vrms   | 90.0     | 90    | 90.0     |                                                                                                                                                                  |

| L of inductor                                     | 7%            | μН     | 158.1    | 170   | 181.9    |                                                                                                                                                                  |

| dl/dt max. rising at                              |               | 122    |          |       |          | di,                                                                                                                                                              |

| V_in peak                                         |               | A/µs   | 0.700    | 0.749 | 0.805    | $\frac{di}{dt} = V/L$                                                                                                                                            |

| ⊥ due to<br>propagation delay                     |               | A      | 0.486    | 0.696 | 0.940    | $\Delta i = \frac{V}{L} (t_{int} + t_{ext} + \tau)$                                                                                                              |

| Calculation of shunt re                           | esistor value | 2      |          |       |          |                                                                                                                                                                  |

| Pout 90Vac                                        |               | W      | 130      |       |          | minimum deliverable output power                                                                                                                                 |

| Efficiency                                        |               |        | 0.93     |       |          | F F                                                                                                                                                              |

| Pin                                               |               | w      | 140      |       |          |                                                                                                                                                                  |

| Vinac min                                         |               | v      | 90       |       |          |                                                                                                                                                                  |

| Ipk_power                                         |               | A      | 4.393    |       |          | $I_{pk_power} = 2\sqrt{2} \frac{p_{in}}{v_{in}}$                                                                                                                 |

| due to propagation                                |               | -      | 10000000 |       |          | Vin                                                                                                                                                              |

| delay Iocp_level                                  |               | Α      | 3.907    |       |          | $I_{OCP\_level} = I_{pk\_power} - \Delta I$                                                                                                                      |

| R_shunt                                           |               | mΩ     | 131      |       |          |                                                                                                                                                                  |

| R_shunt                                           | 5%            | mΩ     | 111.6    | 124   | 131      | selected actual shunt resistance value                                                                                                                           |

| Calculation of current                            | and power     | tolenc | e        |       |          |                                                                                                                                                                  |

| lpk_power                                         |               | Α      | 4.393    | 5.34  | 6.584    |                                                                                                                                                                  |

| lpk_power with                                    |               |        | 1004     |       | 0001     |                                                                                                                                                                  |

| tolerance                                         |               |        | -18%     | 5.34  | 23%      |                                                                                                                                                                  |

| Pout 90Vac                                        |               |        | 130      | 158   | 195      |                                                                                                                                                                  |

| Pout with tolerance                               |               |        | -18%     | 158   | 23%      |                                                                                                                                                                  |

#### Figure 12 Accurate calculation of OCP tolerance

Application Note

It can be seen from the calculation that the actual tolerance of current and power can be very high. Methods to reduce tolerances include:

- Reduce the tolerance of the shunt resistor

- Reduce the tolerance of the PFC choke

- Reduce the value of R and C for the RC filter to reduce the delay

The above calculation is accurate, but is relatively complicated, and requires input data from actual measurements on a real power board (e.g. external propagation delay). A faster and simpler way to obtain a value for the current sense resistor is for customers to use the spreadsheet calculation to finalize the value after the power board is built.

$$R_{PFC\_CS} < \frac{V_{OCP\_PFC} * (1 - g_{error}) * g_{filter}}{I_{pk} * (1 - \Delta_{delay})} = \frac{0.6 * 0.94 * 0.9}{4.39 * (1 - 0.1)} = 0.13 \,\Omega$$

Where  $g_{error}$  is the OCP threshold gain error,  $g_{filter}$  is the gain of RC filter and  $\Delta_{delay}$  is the estimated error due to the internal and external propagation delay.

## 3.3.4.2 Verification of PFC inductance with OCP tolerance

The maximum peak current allowed by the OCP (considering the tolerance) can be obtained from the spreadsheet calculation results and then applied to the equation below to verify the  $B_{max}$  of the PFC inductance:

$$B_{max} = \frac{i_{pk} * L_{PFC}}{N_{PFC}A_{min}} = \frac{6.7 * 200}{39 * 99} = 0.34 T$$

This value is less than the saturation magnetic flux density (B) of 0.35 T (PC40 magnetic material). Therefore, the PFC choke will not saturate under worst case conditions.

## 3.3.5 Frequency law for multi-mode PFC

## 3.3.5.1 Multimode PFC

For a PFC circuit operating in Critical Conduction Mode (CrCM), the MOSFET is turned on with a constant ontime throughout the complete AC half cycle and the off-time varies during the AC half cycle depending on the instantaneous input voltage applied. A new switching cycle starts just after the inductor current reaches zero. CrCM is also equivalent to quasi-resonant switching at the first inductor current valley or QR1 operation.

CrCM is ideal for full load operation, where the constant on-time is large. However, the constant on-time reduces at light load, resulting in very high switching frequency - particularly near the zero crossings of the input voltage. The high switching frequency will increase the switching losses, resulting in poor efficiency at light load.

The multimode PFC control can lower the switching frequency by adding an additional delay ( $t_w$ ) into each switching cycle through selecting further inductor current valleys (matching also with valleys of  $V_{DS}$  of MOSFET) to achieve QR2, QR3 and up to QR10 operation. Figure 13 illustrates the QR2 valley switching in multimode PFC control as an example.

## Design guide IDP2303(A)

#### PFC design

Figure 13 Current and timing in QR2 operation

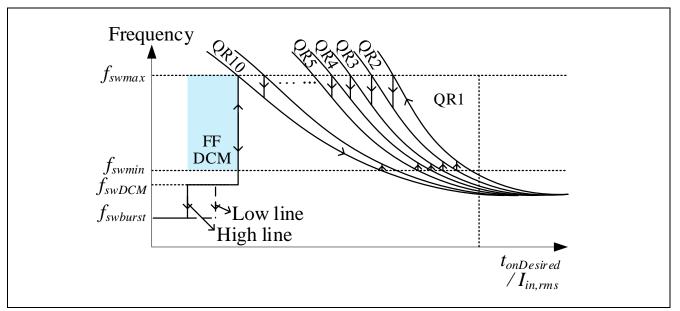

## 3.3.5.2 Frequency law

A frequency law consisting of a maximum switching frequency  $f_{swmax}$  and the minimum switching frequency  $f_{swmin}$  is defined for the valley selection (QRN). In this way, the switching frequency is limited to the defined range and efficiency at light load can be improved. An illustration of the frequency law is shown in Figure 14.

## Design guide IDP2303(A) PFC design

Figure 14 Frequency law for selecting operating modes

The real-time operation of QRN is executed by the IDP230x hardware peripheral QR-timer. A new switching cycle of QRN operation starts with the N-th valley detection of the sensed inductor voltage or with the end of the maximum switching period, whichever occurs first. As illustrated in Figure 13, occurrence of the N-th valley is determined by the N-th falling edge of the ZCD comparator plus a propagation delay that is equivalent to  $T_{osc}/4$  to reach the valley switching point.  $T_{osc}$  is the resonance period of the oscillation due to the PFC inductor and the parasitic capacitance across the MOSFET after the end of boost inductor demagnetization time.

The changing of QRN in multimode control is dependent on the frequency law. When the switching frequency reaches the min frequency, the frequency law defines that the frequency is too low and the switching frequency must increase by reducing the QRN. When the switching frequency reaches the maximum frequency, the frequency law defines that the frequency is too high and switching frequency must reduce by increasing the QRN. The changing of QRN within each AC half cycle is dependent on both the load and AC line, and is inherent in multimode PFC control.

## 3.3.5.3 Setting of $f_{min}$ and $f_{max}$

The setting of minimum and maximum frequencies of the frequency law needs to meet the application requirement that in the condition where  $V_{IN} = 90 V_{AC}$ , full load, the PFC should operate with QR1 mode operation over the whole AC cycle.

From the equation defining the switching frequency with QR1 operation

$$f = \frac{v_{in} * (v_{bus} - v_{in})}{v_{bus} * L_{PFC} * i_{in}}$$

It can be concluded that over the AC cycle, the switching frequency is at a minimum at AC peak and at a maximum at zero crossing. The same applies to QR2 operation.

Therefore, selection rule for  $f_{min}$  is : A value above the maximum switching frequency at the peak of the AC input voltage with QR2 operation and minimum PFC inductance should be selected to force QR1 operation. Selection rule for  $f_{max}$  is: A value above the maximum switching frequency near the zero crossing of the AC input voltage with QR1 operation and minimum PFC inductance should be selected to keep QR1 operation.

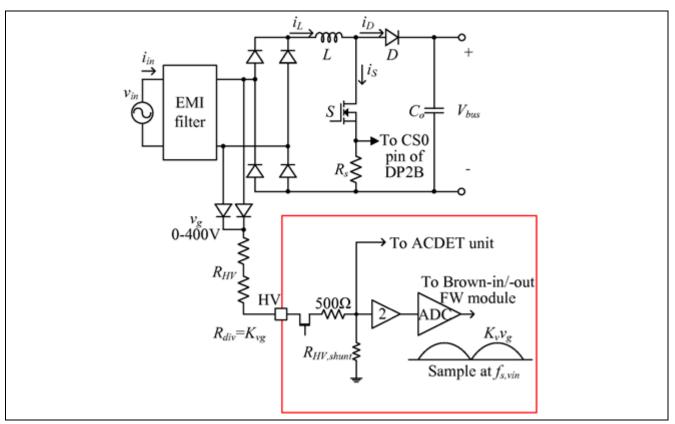

## 3.3.6 AC brown-in & out

The PFC brown-in & out protections prevent the system from starting up or operating at very low input voltage outside the designed operating range. For a system without input brown-in & out protection, the boost converter may draw a higher current from the mains at a given output power which may lead to overheating of the MOSFET and boost diode. PFC brown-in & out protections are implemented by firmware and utilize the HV pin for AC input voltage sampling.

Figure 15 Sampling of the rectified AC input voltage

The rectified AC input voltage V<sub>g</sub> is measured using the HV pin of the IDP230X across an internal shunt resistor as shown in Figure 15. The internal shunt resistor R<sub>HV</sub>, shunt (set to 125  $\Omega$ ), internal 500  $\Omega$  series resistor and the external R<sub>HV</sub> resistors (to save design effort, a value of 51k  $\Omega$ , with 1% tolerance is advised) form a resistor divider with the ratio K<sub>vg</sub>. There is an internal op-amp with a fixed gain of 2. Thus, the magnitude of the sensed input voltage at the ADC buffer is given by:

$$v_{g\_ADC} = 2K_{vg}v_g = 2\frac{R_{HV\_shunt}}{R_{HV} + 500 + R_{HV\_shunt}}v_g = 2\frac{125}{51 \times 10^3 + 500 + 125}v_g = 4.84 \times 10^{-3}v_g$$

For ease of implementation, the RMS input voltage  $v_{g_{-rms}}$  is estimated from the peak value  $v_{g_{-ADC_pk}}$  of the sampled input voltage.

If  $v_{g_rms}$  exceeds the desired brown-in input voltage threshold, brown-in is detected and the system enters startup.

If  $v_{g_rms}$  falls below the desired brown-out input voltage threshold then, after a blanking time, brown-out is detected. The PFC will stop switching immediately.

The brown-in and out thresholds are set as 70  $V_{AC}$  and 60  $V_{AC}$  and they are configurable via dpVision.

# 4 LLC design

## 4.1 Target specifications

The LLC target specifications are summarized in Table 6.

| Table 6 | Design parameters for the LLC design |

|---------|--------------------------------------|

|---------|--------------------------------------|

| Parameter          | Symbol             | Value  | Unit |  |

|--------------------|--------------------|--------|------|--|

| Bus bulk capacitor | C <sub>bulk</sub>  | 68 x 2 | μF   |  |

| Output voltage     | V <sub>0_24</sub>  | 24     | V    |  |

| Output current     | I <sub>0_24</sub>  | 3.5    | А    |  |

| Output voltage     | V <sub>0_12</sub>  | 12     | V    |  |

| Output current     | I <sub>0_12</sub>  | 3      | А    |  |

| Output power       | P <sub>o_LLC</sub> | 120    | W    |  |

| LLC efficiency     | η <sub>ιιc</sub>   | 93%    |      |  |

| Resonant frequency | fr                 | 100    | kHz  |  |

| Hold up time       | t <sub>hold</sub>  | 20     | ms   |  |

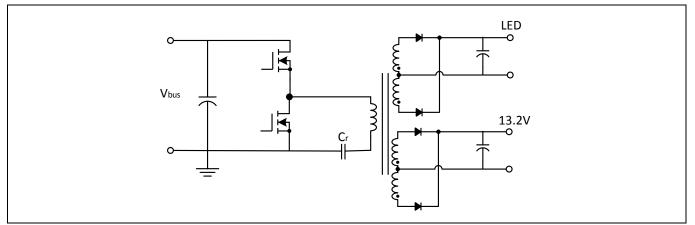

## 4.2 Power stage

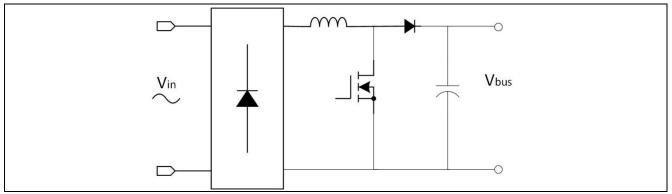

A simplified application circuit for the LLC stage is given in Figure 16 :

Figure 16 Simplified circuit for LLC converter

## 4.2.1 System parameter calculation

Based on the required 20 ms hold-up time for the system, the minimum operation voltage for the LLC stage can be calculated as:

$$V_{bus\_min} = \sqrt{V_{bus}^2 - \frac{2P_{o\_LLC}T_{hold}}{\eta C_{bulk}}} = \sqrt{390^2 - \frac{2*120*20*10^{-3}}{0.93*68*2*10^{-6}}} = 337 V$$

## 4.2.2 Main transformer and resonant network

## 4.2.2.1 Transformer turns ratio

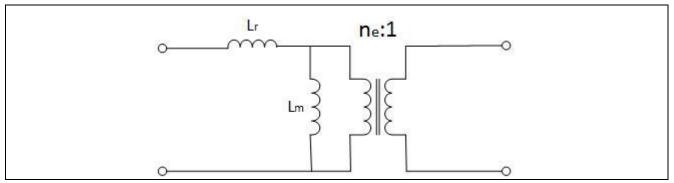

In this design, an integrated transformer is considered, where the leakage inductance is used as a series inductor, while the magnetizing inductor is used a shunt inductor. The all-primary-referred model of the transformer is shown in Figure 17, where  $n_e$  is the equivalent turns ratio. All the elements related to leakage flux are located on the primary side.

Figure 17 Transformer primary referred model

When a separate resonant inductor is used, the equivalent turns ratio  $n_e$  is equal to the physical turns ratio. With an integrated resonant inductor, the equivalent turns ratio  $n_e$  is less than the physical turns ratio, due to the leakage inductance in the transformer secondary.

The equivalent turns ratio can be estimated as:

$$n_e = \frac{n}{M_v}$$

where

$$M_v = \sqrt{\frac{m}{m-1}}$$

*m* is the ratio between the primary inductance  $L_p$  (=  $L_m + L_r$ ) and resonant inductance  $L_r$ :

$$m = L_p/L_r$$

In this design example, m = 4.35 is pre-selected as a starting point, based on the transformer bobbin available and the rule of thumb. Verification and optimization is required for a given implementation, switching frequency and design power level. Guidance on selection will be provided in a later section. The required equivalent turns ratio can be calculated as:

$$n_e = \frac{V_{bus\_nom}}{2(V_o + V_f)} = \frac{390}{2(24 + 0.5)} = 8$$

Assuming the forward voltage drop of secondary-side rectifier diode  $V_f = 0.5 V$ .

Correspondingly the physical turns ratio of the transformer *n* will be -

$$n = n_e M_v = n_e \sqrt{\frac{m}{m-1}} = 8 * 1.14 = 9.1$$

Consider that, in an actual design, n is adjusted to be 8.5. Then the corresponding  $n_e$  is 7.5. The corresponding gain at nominal input voltage is

$$M_{nom} = \frac{2(V_o + V_f)n_e}{V_{bus\_nom}} = 0.94$$

Application Note

The maximum voltage gain  $M_{max}$  required is during conditions of full load operation at minimum input voltage  $V_{bus\_min}$ , which can be calculated as:

$$M_{max} = \frac{V_{bus\_nom}}{V_{bus\_min}} M_{nom} = \frac{390}{338} 0.94 = 1.08$$

### 4.2.2.2 Equivalent circuit and resonant network

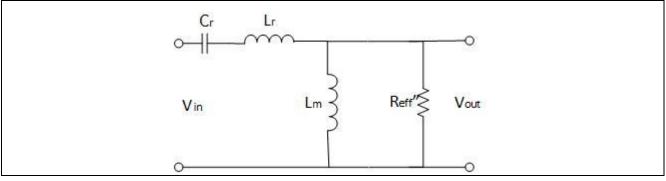

All analysis and calculation in this section is based upon the equivalent circuit in Figure 18 that can be derived with the First Harmonic Approximation (FHA) modelling methodology.

Figure 18 Equivalent circuit

If the total output load is referred to 24 V, the effective load resistance can be given as:

$$R_{eff} = \frac{8}{\pi^2} n_e^2 \frac{V_o}{I_o} = \frac{8}{\pi^2} 7.55^2 \frac{24}{5} = 216 \,\Omega$$

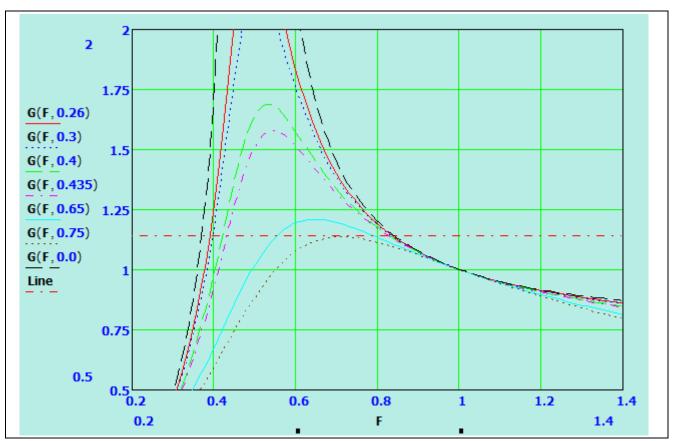

Defining the normalised frequency  $f_r$  is  $F = \frac{f}{f_r}$ , the load factor of the LLC converter is  $Q_e = \frac{\sqrt{\frac{L_r}{C_r}}}{\frac{R_{eff}}{R_{eff}}}$ , the voltage gain of the converter can be obtained based on the equivalent circuit Figure 19:

$$M_j(F,Q) = \frac{F^2(m-1)}{(F^2m-1) + jF(F^2-1)(m-1)Q_e}$$

Its magnitude is:

$$G(F,Q) = \sqrt{Re(M_j(F,Q_e))^2 + Im(M_j(F,Q_e))^2}$$

The graph of voltage gain G vs F for different values of Q can be plotted as in Figure 19, based on the equation above:

Design guide IDP2303(A) LLC design

Figure 19 Voltage gain G Vs normalized frequency F

The curve where Qe = 0.75 can achieve the required peak gain,  $G_{pk}$ , which is  $M_{max}$ ,  $G_{pk} = M_{max} * 1.05 = 1.14$

Having found the proper Qe, we can calculate  $C_r$ ,  $L_r$  and  $L_p$  as follows:

$$C_r = \frac{1}{2\pi * Qe * f_{r*}R_{eff}} = \frac{1}{2\pi * 0.75 * 100 * 10^3 * 218} = 9.8 \, nF$$

If a 10 nF capacitor is selected as  $C_r$ , then, in the actual design, Qe must be re-calculated as

$$Qe = \frac{1}{2\pi * C_r * f_{r*}R_{eff}} = 0.74$$

$$L_r = \frac{1}{(2\pi f_r)^2 C_r} = \frac{1}{(2\pi * 100 * 10^3)^2 * 10 * 10^{-9}} = 253 \ uH$$

$$L_p = mL_r = 1.1 \ mH$$

The value of  $L_p$  can be achieved by adjusting the gap length.

From the gain curve with Qe = 0.74 in Figure 19, the normalized frequency  $F_{min} = 0.87$  can be located to achieve the required maximum gain  $G_{pk} = 1.08$ , for the condition of minimum input voltage at full load. Accordingly, the actual minimum frequency  $f_{min}$  is:

$$f_{min} = F * f_r = 0.87 * 100 = 87 \ kHz$$

Similarly, the normalized frequency  $F_{nom} = 1.1$  can be located to achieve gain,  $G = M_{nom} = 0.94$  for nominal input voltage at full load. Accordingly, the actual nominal frequency  $f_{nom}$  is:

$$f_{nom} = F * f_r = 1.1 * 100 = 110 \ kHz$$

infineon

## 4.2.2.3 Calculation of transformer turn ratio

In the above section, the actual minimum frequency  $f_{min}$  has been calculated as 87 kHz.

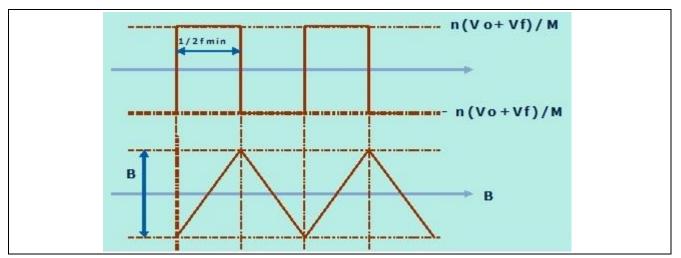

Figure 20 Flux density swing

According to the flux density swing illustrated in Figure 20, the voltage across the primary winding can be calculated as  $V_p = n_e (V_o + V_f)$ . The half switching cycle period is around  $t = \frac{1}{2f}$ . According to Faraday's law:

$$\frac{n_e(V_o + V_f)}{2f} = N_p A_e \Delta B$$

The number of turns on the primary side can be found by:

$$N_P = \frac{n_e(V_o + V_f)}{2f * A_e \Delta B}$$

Where  $A_e = 88 mm^2$  with an EFD38 core.  $\Delta B = 0.62T$  is selected to avoid magnetic saturation. Then  $N_{pmin}$  can be calculated at minimum bus voltage  $V_{bus\_min}$  by:

$$N_{pmin} = \frac{n_e(V_o + V_f)}{2f_{min} * A_e \Delta B} = \frac{7.5 * (24 + 0.5)}{2 * 87 * 10^{-3} * 88 * 10^{-6} * 0.62} = 20$$

The selection of the number of turns on the primary side must also take other factors into consideration. For example, to minimize the circulating current in the primary side due to the magnetizing current, a relatively larger magnetizing inductance is preferred. Furthermore, the number of turns on the secondary side for 24 V and 12 V should be integers. The selection is also limited by the structure of the EFD38 transformer available. Lastly, the number of turns on the primary side is selected as  $N_p = 51$ . The secondary side turns for 24 V and 12 V can then be calculated accordingly by:

$$N_{s_{2}24V} = \frac{N_{p}}{n} = 6$$

$$N_{s_{1}2V} = \frac{N_{s_{2}24V}}{2} = 3$$

LLC design

## 4.2.2.4 Selection of resonant factor m

Numerous factors come into play while considering the value of the resonant factor *m*.

$$m = \frac{L_p}{L_r} = \frac{L_m + L_r}{L_r}$$

In order to achieve the highest efficiency possible, the magnetizing inductance  $L_m$  should be set to be large. Therefore, the magnetizing current  $I_{mag}$  is small for the specified value of bus voltage and switch-on time, thus allowing for low core and conduction loss in transformer.

$$I_{mag} = \frac{1}{4} \frac{V_{bus} t_{on}}{L_m}$$

On the other hand, the magnetizing current must be large enough to charge and discharge the output capacitance  $C_{sw}$  of the primary side MOSFET during the deadtime  $t_{dt}$ , to achieve ZVS and thus ensure safe switching and reduce switching losses.

$$I_{mag} \cong \frac{V_{bus} C_{sw}}{t_{dt}}$$

Furthermore, sufficient magnetizing current is required to ensure that the MOSFET body diode can complete reverse recovery during turn-on at light load [4].

The value of the resonant factor m also has an effect on the shape of gain curves and the attainable maximum gain. Larger values of m result in flatter gain curves which leads to a wider operation frequency range.

In the real world, the selection of m is also limited by the structure of the selected transformer, which determines the value of the leakage inductance  $L_r$ . Therefore, determining the value of m can be an iterative process involving many factors.

## 4.2.2.5 Selection of resonant capacitor

The current through the resonant capacitor is the sum of the magnetizing current and the load current referred to the primary. Its RMS value can be calculated as:

$$\begin{split} I_{C_{r\_}rms} &= \frac{1}{\eta} \sqrt{(\frac{\pi I_o}{2n_e\sqrt{2}})^2 + \left[\frac{n_e(V_o + V_F)}{4\sqrt{2}f_{nom}M_{nom}(L_p - L_r)}\right]^2} \\ &= \frac{1}{0.93} \sqrt{(\frac{\pi * 5}{2 * 7.5\sqrt{2}})^2 + \left[\frac{7.5 * (24 + 0.5)}{4\sqrt{2} * 110 * 10^3 * 0.94 * 847 * 10^{-6}}\right]^2} = \frac{1}{0.93} \sqrt{0.74^2 + 0.37^2} \\ &= 0.89 \,A \end{split}$$

The voltage across the resonant capacitor reaches a peak at the over current trigger point (OCP), which is estimated to have a 65% margin over the peak current in the primary side during normal operation. The accurate maximum OCP trigger point, including consideration of the tolerance is calculated in section 4.3.2.

$$I_{ocp} = \sqrt{2}I_{C_{r\_}rms}(1 + 65\%) = 2.1 \,A$$

$$V_{C_r} \cong \frac{V_{bus}}{2} + \frac{I_{ocp}}{2\pi f_{min}C_r} = \frac{390}{2} + \frac{2.1}{2\pi * 100 * 10^3 * 10 * 10^{-9}} = 529 V$$

A 630 V rated low-ESR film capacitor is selected as the resonant capacitor.

## 4.2.3 Power MOSFET selection

It is important to select the correct MOSFET; not only for the efficiency but also for the reliability of an LLC resonant converter [4]. In addition to the basic criteria such as package, drain-source voltage rating, drain current rating and on-state resistance, two considerations are required for power MOSFET selection and driving signal design in an LLC resonant converter:

- maintenance of Zero Voltage Switching (ZVS) operation of the power MOSFET;

- avoidance of system reliability issues due to incomplete body diode reverse recovery in the power MOSFET

Infineon high voltage MOSFETs have several families based on different technologies, which each target a specific application, topology or operation. Several CoolMOS<sup>™</sup> series can be used for boost applications depends on customer's requirement for the voltage rating, thermal characteristic etc.

With the CE in 500 V, E6 and P6 family in 600 V, Infineon offers series with extremely low conduction and switching losses and can make switching applications more efficient, more compact, lighter and cooler.

The IPD50R1K4CE is pre-selected for the design and the conduction loss is calculated as below.

The maximum drain current through the MOSFET is the same as that through the resonant capacitor.

$$I_{Q2\_RMS} = I_{C_{r \ rms}} = 0.89 \, A$$

$$P_{con} = I_{Q2\_rms}^2 R_{DS_{on}} = 0.89^2 * 2.5 = 1.98 W$$

$R_{DS_{on}} = 2.5 \Omega$  is the on-state resistance of MOSFET at junction temperature of 100°C.

## 4.2.4 MOSFET gate driving

Similar to the PFC gate driver, the LLC low side gate driver offers unique features such as configurable charge current and output voltage.

The recommended  $R_{gate}$  values for different application cases with all possible values of  $C_{gate}$ ,  $R_{gs}$  and gatesource current are summarized below in Table 7. As a rule-of-thumb, a 10  $\Omega$  gate resistor generally fits for most application cases.

| C <sub>gate</sub> (nF)              |      | 0.4~2.0 |      |       |      |       |  |  |

|-------------------------------------|------|---------|------|-------|------|-------|--|--|

| gate source current (mA)            | 3    | 30      |      | 73    |      | 120   |  |  |

| R <sub>gs</sub> (Ω)                 | 10 k | 100 k   | 10 k | 100 k | 10 k | 100 k |  |  |

| Recommended $R_{gate}$ ( $\Omega$ ) | 5~30 | 5~35    | 5~25 | 5~25  | 5~15 | 5~15  |  |  |

Table 7

Recommended Rgate values for different Cgate, Rgs and gate source current

The LLC high side gate driver is an integrated floating driver based on coreless transformer technology. To generate a balanced gate driving signal (rise/fall time) with a low side to avoid shoot-through and other possible problems, a larger gate resistor is usually required (approximately 120  $\Omega$ ). The customer can fine-tune the value by monitoring the gate and other signals at the high and low side to ensure safe operation.

## 4.2.5 Output rectifier

The voltage stress on the 12 V and 24 V output rectifier diodes are:

$$V_{D_{-12}} = 2 * (V_o + V_f) = 2 * (12 + 0.5) = 25 V$$

$$V_{D_{-24}} = 2 * (V_o + V_f) = 2 * (24 + 0.5) = 49 V$$

The RMS value of the current flowing through each diode is:

$$I_{D\_rms\_12} = \frac{\pi}{4}I_o = \frac{\pi}{4} * 3 = 2.36 A$$

$$I_{D\_rms\_24} = \frac{\pi}{4}I_o = \frac{\pi}{4} * 3.5 = 2.75 A$$

Considering the voltage overshoot due to the stray inductance, 60 V/20 A and 100 V/30 A Schottky diodes are selected as the rectifier diodes for the 12 V and 24 V channels, repectively.

## 4.3 Control parameters and protections

## 4.3.1 VCO frequency curve

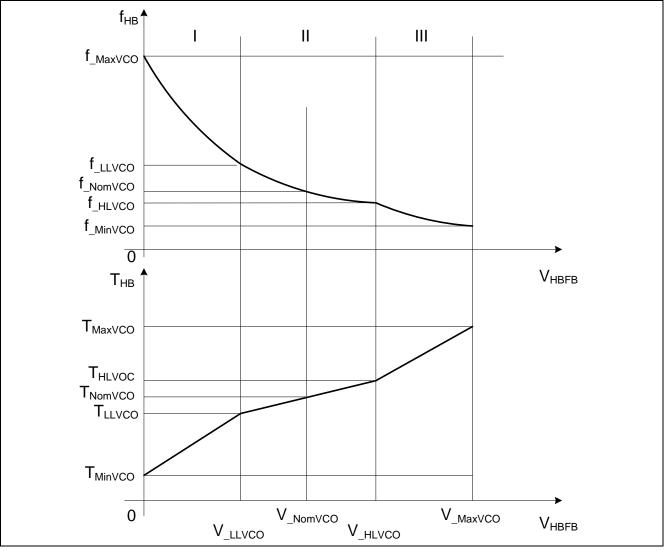

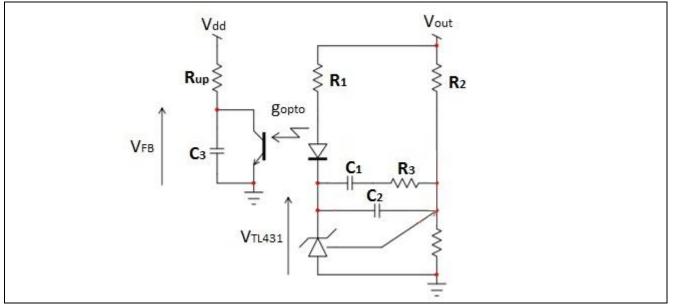

During normal LLC operation, a voltage-controlled oscillator (VCO) generates the LLC converter switching frequency  $f_{HB}$  based on the average LLC feedback voltage  $V_{HBFB}$ .

With a DP digital controller, a VCO curve based on switching period can be easily implemented digitally. The curve of the LLC switching period  $T_{HB}$  with respect to the feedback voltage  $V_{HBFB}$  is shown in the figure below.

Figure 21 VCO curve

The VCO curve consists of three linear sections with different slew rates. As shown in the lower half of Figure 21, the line in area II (normal operation) has much lower slew rate than the line in areas I (light load) and III

(heavy load). Therefore, the VCO in the area II has a much better frequency resolution than in the area I and III. In this way, fine frequency resolution around the nominal operating point  $V_{\text{NomHB}}$  is realized, while a wide operating frequency range can be covered with fast response to the load change in both heavy and light load is realized.

To define a proper VCO, 4 key points have to be determined.

- $V_{MinVCO}$ :  $f_{MaxVCO}$  (feedback origin)

- V<sub>LLVCO</sub> : f<sub>LLVCO</sub> (light load)

- $V_{HLVCO}$  :  $f_{HLVCO}$  (heavy load)

- $V_{MaxVCO}$  :  $f_{MaxVCO}$  (feedback maximum)

Once these points are defined, the switching period is calculated by a linear interpolation of the switching period to the feedback voltage, and the switching frequency curve over the whole feedback range is generated, which is naturally a non-linear function of the feedback voltage, as shown in Figure 21.

## 4.3.1.1 $V_{\_MinVCO}$ and $V_{\_MaxVCO}$

The minimum and maximum voltages are determined by the hardware configuration. For example, the IDP230x IO pullup voltage range is 0~3.3 V, and the ADC range is 0~2.4 V, thus the full VCO range should be within 0~2.4 V.

# 4.3.1.2 $f_{MinVCO}$ and $f_{MaxVCO}$

The frequency,  $f_{MinVCO}$  is determined by the operating condition where full load is applied at minimum bus voltage during the hold-up time. Under this condition, the maximum gain is achieved at the minimum switching frequency,  $f_{min}$ . It can be derived that:

$$f_{MinVCO} = f_{min} = 87 \ kHz$$

The maximum operation frequency  $f_{MaxVCO}$  can possibly be seen when the maximum input voltage (threshold value of OVP1, say 420 V) is applied, and the converter is run at a no load condition (Q = 0), if burst mode is disabled. The gain in this condition can be given as:

$$M_{min} = \frac{V_{bus\_nom}}{V_{bus\_max}} M_{nom} = \frac{390}{420} * 0.94 = 0.87$$

From the gain equation, we get:

$$G(F,Q) = \frac{F^2(m-1)}{(F^2m-1)} = M_{\min}, (Q=0)$$