TIC12400-Q1 SCPS260A -AUGUST 2017-REVISED SEPTEMBER 2017

# TIC12400-Q1 24-Input Multiple Switch Detection Interface (MSDI) With Integrated ADC and Adjustable Wetting Current for Automotive Systems

#### **Features**

- Qualified for Automotive Applications

- AEC-Q100 Qualified With the Following Results:

- Device Temperature Grade 1: –40°C to 125°C **Ambient Operating Temperature**

- Device HBM ESD Classification Level H2

- Device CDM ESD Classification Level C4B

- Designed to Support 12-V Automotive Systems with Over-voltage and Under-voltage Warning

- Monitors up to 24 Direct Switch Inputs with 10 Inputs Configurable to Monitor Switches Connected to Either Ground or Battery

- Switch Input Withstands up to 40 V (Load Dump Condition) and down to -24 V (Reverse Polarity Condition)

- 6 Configurable Wetting Current Settings: (0 mA, 1 mA, 2 mA, 5 mA, 10 mA, and 15 mA)

- Integrated 10-bit ADC for Multi-Position Analog Switch Monitoring

- Integrated Comparator with 4 Programmable Thresholds for Digital Switch Monitoring

- Ultra-low Operating Current in Polling Mode: 68 μA Typical ( $t_{POLL}$  = 64 ms,  $t_{POLL\_ACT}$  = 128 μs, All 24 Inputs Active, Comparator Mode, All Switches Open)

- Interfaces Directly to MCU Using 3.3 V / 5 V Serial Peripheral Interface (SPI) Protocol

- Interrupt Generation to Support Wake-Up Operation on All Inputs

- Integrated Battery and Temperature Sensing

- ±8 kV Contact Discharge ESD Protection on Input Pins per ISO-10605 With Appropriate External Components

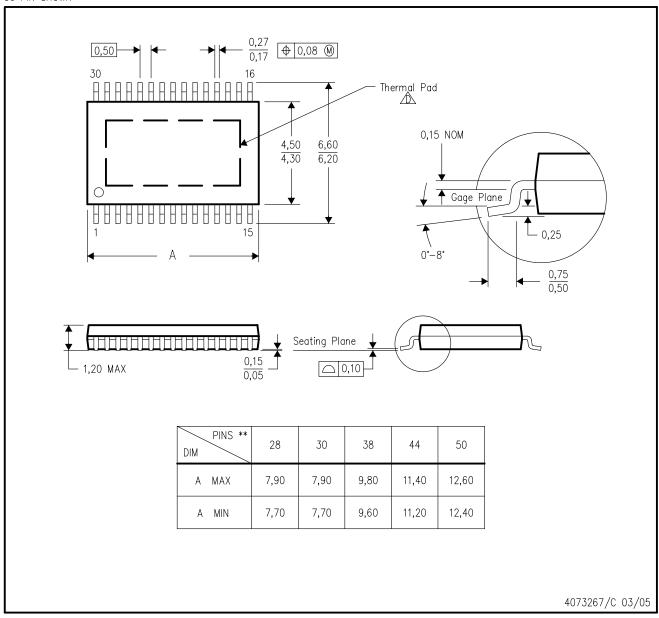

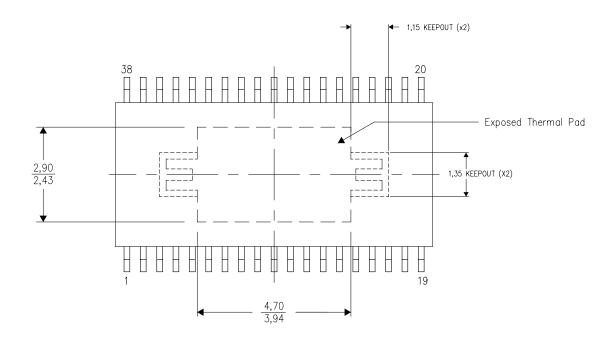

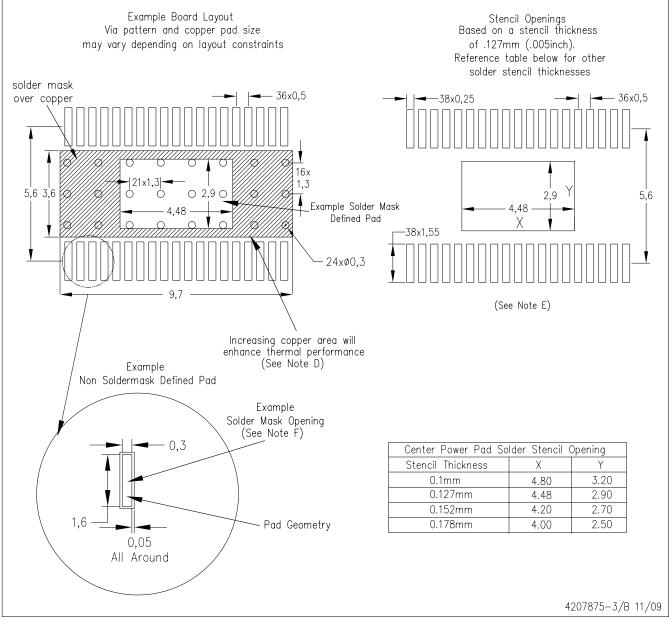

- 38-Pin TSSOP Package

# Applications

- Body Control Module and Gateway

- Automotive Lighting

- Heating and Cooling

- **Power Seats**

- Mirrors

# 3 Description

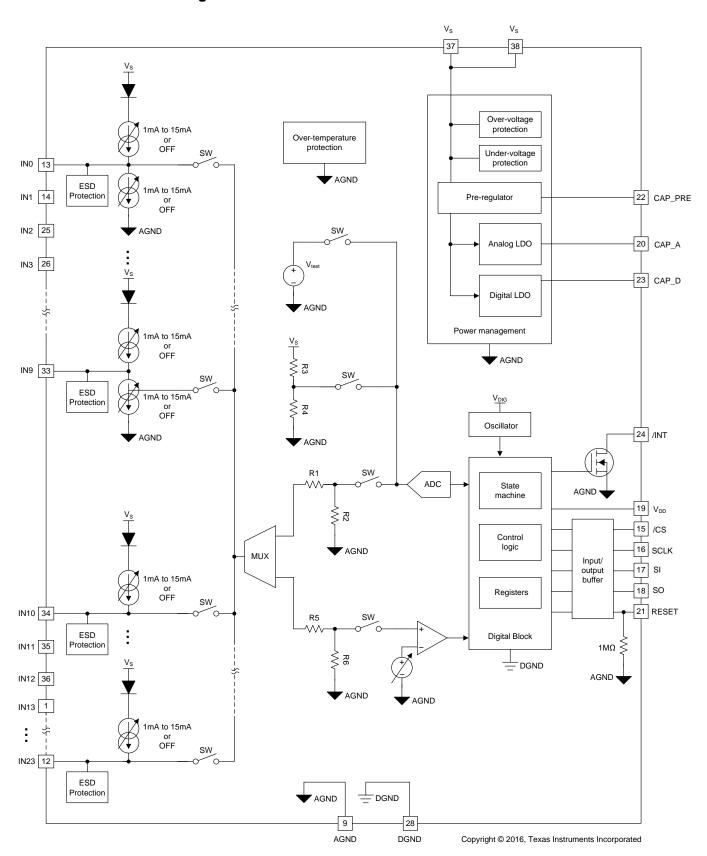

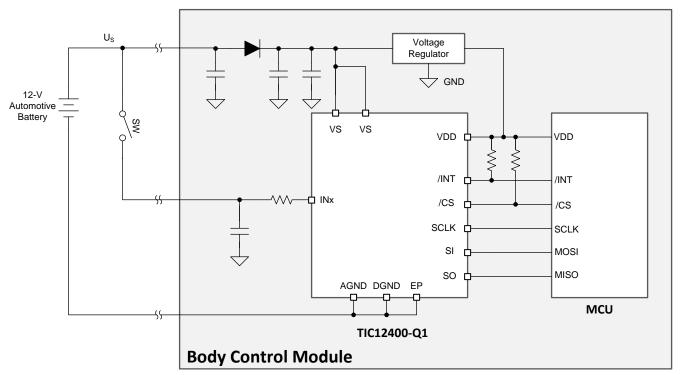

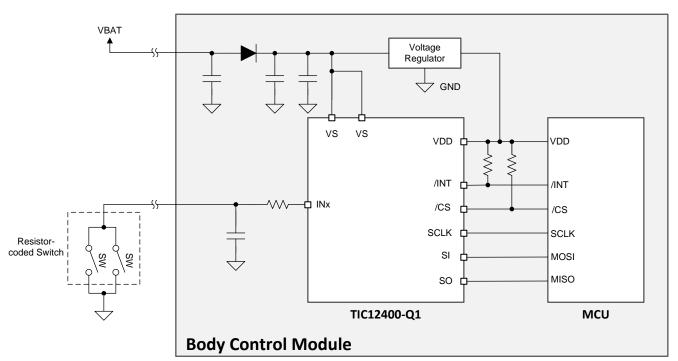

The TIC12400-Q1 is an advanced Multiple Switch Detection Interface (MSDI) designed to detect external switch status in a 12-V automotive system. The TIC12400-Q1 features an integrated 10-bit ADC to monitor multi-position analog switches and a comparator to monitor digital switches independently MCU. Detection thresholds programmed for the ADC and the comparator to support various switch topologies and system nonidealities. The device monitors 24 direct switch inputs, with 10 inputs configurable to monitor switches connected to either ground or battery. 6 unique wetting current settings can be programmed for each input to support different application scenarios. The device supports wake-up operation on all switch inputs to eliminate the need to keep the MCU active continuously, thus reducing power consumption of the system. The TIC12400-Q1 also offers integrated fault detection, ESD protection, and diagnostic functions for improved system robustness. The TIC12400-Q1 supports 2 modes of operations: continuous and polling mode. In continuous mode, wetting current is supplied continuously. In polling mode, wetting current is turned on periodically to sample the input status based on a programmable timer, thus the system power consumption is significantly reduced.

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE    | BODY SIZE (NOM)   |  |  |

|-------------|------------|-------------------|--|--|

| TIC12400-Q1 | TSSOP (38) | 9.70 mm x 4.40 mm |  |  |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

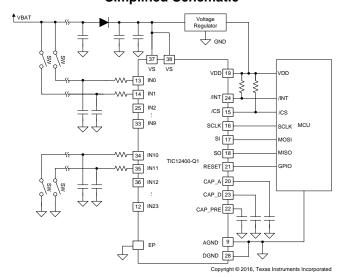

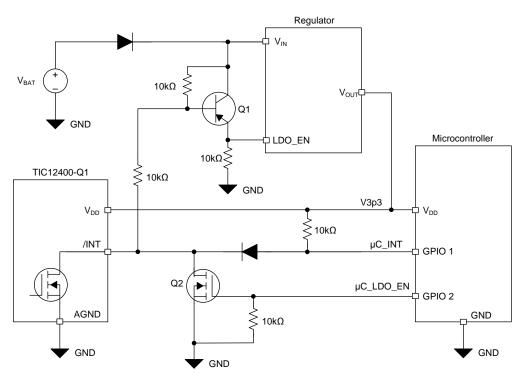

#### Simplified Schematic

# **Table of Contents**

| 1 | Features 1                                      |     | 8.6 REGISTER_MAPS                                                       |     |

|---|-------------------------------------------------|-----|-------------------------------------------------------------------------|-----|

| 2 | Applications 1                                  |     | 8.7 Programming Guidelines                                              |     |

| 3 | Description 1                                   | 9   | Application and Implementation                                          | 115 |

| 4 | Revision History2                               |     | 9.1 Application Information                                             | 115 |

| 5 | Pin Configuration and Functions                 |     | 9.2 Using TIC12400-Q1 in a 12 V Automotive System                       | 115 |

| 6 | Specifications 5 6.1 Absolute Maximum Ratings 5 |     | 9.3 Resistor-coded Switches Detection in Automotive Body Control Module |     |

|   | 6.2 ESD Ratings 5                               | 10  | Power Supply Recommendations                                            | 121 |

|   | 6.3 Recommended Operating Conditions 5          | 11  | Layout                                                                  |     |

|   | 6.4 Thermal Information 6                       | • • | 11.1 Layout Guidelines                                                  |     |

|   | 6.5 Electrical Characteristics                  |     | 11.2 Layout Example                                                     | 123 |

|   | 6.6 Timing Requirements                         | 12  | Device and Documentation Support                                        |     |

|   | 6.7 Typical Characteristics                     |     | 12.1 Receiving Notification of Documentation                            |     |

| 7 | Parameter Measurement Information 13            |     | Updates                                                                 | 124 |

| 8 | Detailed Description 14                         |     | 12.2 Community Resources                                                | 124 |

|   | 8.1 Overview 14                                 |     | 12.3 Trademarks                                                         | 124 |

|   | 8.2 Functional Block Diagram 15                 |     | 12.4 Electrostatic Discharge Caution                                    | 124 |

|   | 8.3 Feature Description                         |     | 12.5 Glossary                                                           | 124 |

|   | 8.4 Device Functional Modes                     | 13  | Mechanical, Packaging, and Orderable                                    | 105 |

|   | 8.5 Programming                                 |     | Information                                                             | 125 |

# 4 Revision History

| Cł | nanges from Original (August 2017) to Revision A                                                                                                                     | Page |

|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| •  | Changed the I <sub>WETT</sub> value in the <i>Electrical Characteristics</i> table                                                                                   | 7    |

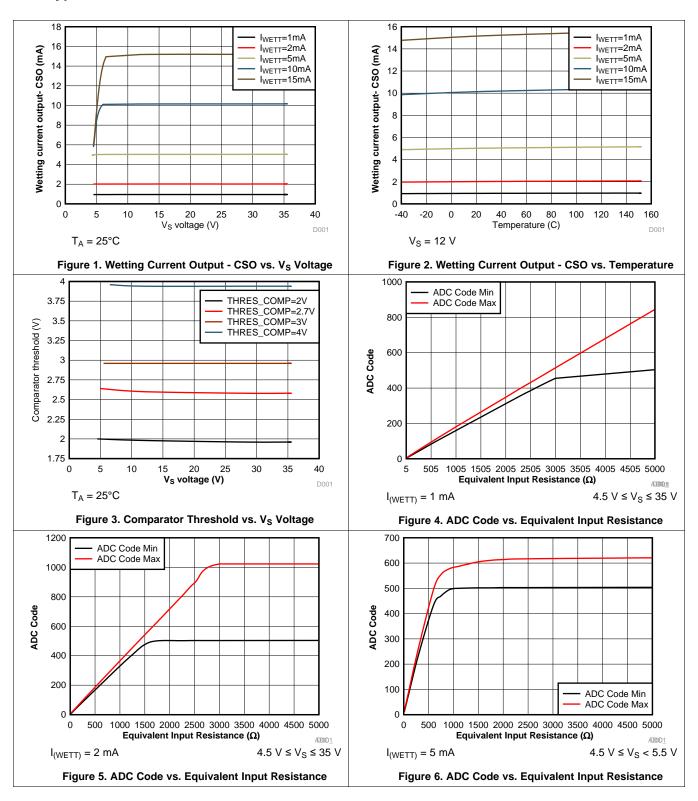

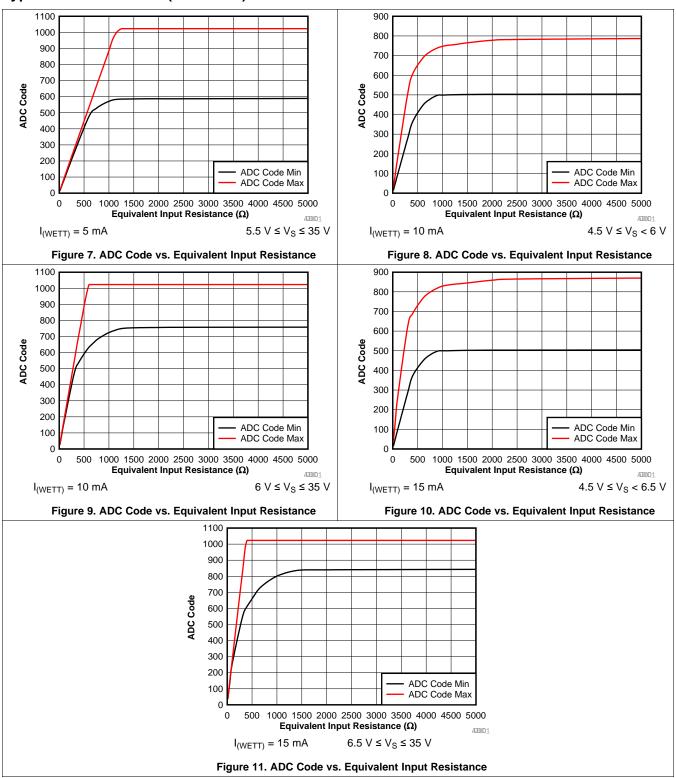

| •  | Changed From: 4.5 V $\leq$ V <sub>S</sub> $\leq$ 5 V To: 4.5 V $\leq$ V <sub>S</sub> $<$ 5.5 V in Figure 6                                                           | 11   |

| •  | Changed From: 4.5 V $\leq$ V <sub>S</sub> $\leq$ 35 V To: 5.5 V $\leq$ V <sub>S</sub> $\leq$ 35 V in Figure 7                                                        | 11   |

| •  | Changed the Microcontroller Wake-Up section, and Figure 23                                                                                                           | 24   |

| •  | Changed Table 64                                                                                                                                                     | 119  |

| •  | Changed text in list item 2 From: "current ranging between 4.3 mA and 5.6 mA." To: "current ranging between 4.5 mA and 5.5 mA (for $V_S - IN_X \ge 3 V$ condition)." | 119  |

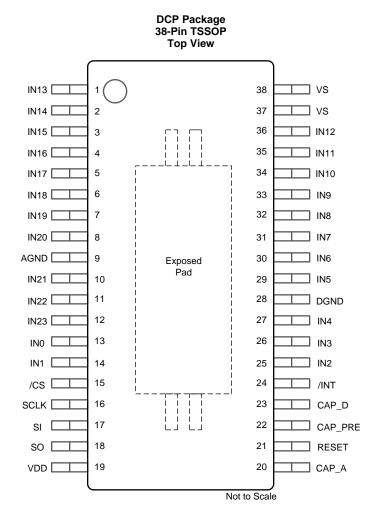

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PIN TYPE <sup>(1)</sup> |      | TVDE(1) | DECEDIPTION                                                                               |

|-------------------------|------|---------|-------------------------------------------------------------------------------------------|

| NO.                     | NAME | ITPE\"  | DESCRIPTION                                                                               |

| 1                       | IN13 | I/O     | Ground switch monitoring input with current source                                        |

| 2                       | IN14 | I/O     | Ground switch monitoring input with current source                                        |

| 3                       | IN15 | I/O     | Ground switch monitoring input with current source                                        |

| 4                       | IN16 | I/O     | Ground switch monitoring input with current source                                        |

| 5                       | IN17 | I/O     | Ground switch monitoring input with current source                                        |

| 6                       | IN18 | I/O     | Ground switch monitoring input with current source                                        |

| 7                       | IN19 | I/O     | Ground switch monitoring input with current source                                        |

| 8                       | IN20 | I/O     | Ground switch monitoring input with current source                                        |

| 9                       | AGND | Р       | Ground for analog circuitry                                                               |

| 10                      | IN21 | I/O     | Ground switch monitoring input with current source                                        |

| 11                      | IN22 | I/O     | Ground switch monitoring input with current source                                        |

| 12                      | IN23 | I/O     | Ground switch monitoring input with current source                                        |

| 13                      | IN0  | I/O     | Ground/V <sub>BAT</sub> switch monitoring input with configurable current sink or source. |

| 14                      | IN1  | I/O     | Ground/V <sub>BAT</sub> switch monitoring input with configurable current sink or source. |

(1) I = input, O = output, I/O = input and output, P = power.

# Pin Functions (continued)

|     | PIN             |                     | PERCEINTION                                                                                                                                                                                                                                                                                                        |  |  |  |

|-----|-----------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NO. | NAME            | TYPE <sup>(1)</sup> | DESCRIPTION                                                                                                                                                                                                                                                                                                        |  |  |  |

| 15  | CS              | I                   | Active-low input. Chip select from the master for the SPI Interface.                                                                                                                                                                                                                                               |  |  |  |

| 16  | SCLK            | I                   | Serial clock output from the master for the SPI Interface                                                                                                                                                                                                                                                          |  |  |  |

| 17  | SI              | I                   | Serial data input for the SPI Interface.                                                                                                                                                                                                                                                                           |  |  |  |

| 18  | SO              | 0                   | Serial data output for the SPI Interface                                                                                                                                                                                                                                                                           |  |  |  |

| 19  | V <sub>DD</sub> | Р                   | 3.3 V to 5.0 V logic supply for the SPI communication. The SPI I/Os are not fail-safe protected: VDD needs to be present during any SPI traffic to avoid excessive leakage currents and corrupted SPI I/O logic levels.                                                                                            |  |  |  |

| 20  | CAP_A           | I/O                 | External capacitor connection for the analog LDO. Use capacitance value of 100nF.                                                                                                                                                                                                                                  |  |  |  |

| 21  | RESET           | I                   | Keep RESET low for normal operation and drive RESET high and release it to perform a hardware reset of the device. The RESET pin is connected to ground via a $1M\Omega$ pull-down resistor. If not used, the RESET pin shall be grounded to avoid any accidental device reset due to coupled noise onto this pin. |  |  |  |

| 22  | CAP_Pre         | I/O                 | External capacitor connection for the pre-regulator. Use capacitance value of 1µF.                                                                                                                                                                                                                                 |  |  |  |

| 23  | CAP_D           | I/O                 | External capacitor connection for the digital LDO. Use capacitance value of 100nF.                                                                                                                                                                                                                                 |  |  |  |

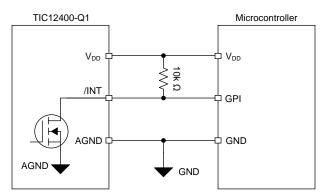

| 24  | ĪNT             | 0                   | Open drain output. Pulled low (internally) upon change of state on the input or occurrence of a special event.                                                                                                                                                                                                     |  |  |  |

| 25  | IN2             | I/O                 | Ground/V <sub>BAT</sub> switch monitoring input with configurable current sink or source.                                                                                                                                                                                                                          |  |  |  |

| 26  | IN3             | I/O                 | Ground/V <sub>BAT</sub> switch monitoring input with configurable current sink or source.                                                                                                                                                                                                                          |  |  |  |

| 27  | IN4             | I/O                 | Ground/V <sub>BAT</sub> switch monitoring input with configurable current sink or source.                                                                                                                                                                                                                          |  |  |  |

| 28  | DGND            | Р                   | Ground for digital circuitry                                                                                                                                                                                                                                                                                       |  |  |  |

| 29  | IN5             | I/O                 | Ground/V <sub>BAT</sub> switch monitoring input with configurable current sink or source.                                                                                                                                                                                                                          |  |  |  |

| 30  | IN6             | I/O                 | Ground/V <sub>BAT</sub> switch monitoring input with configurable current sink or source.                                                                                                                                                                                                                          |  |  |  |

| 31  | IN7             | I/O                 | Ground/V <sub>BAT</sub> switch monitoring input with configurable current sink or source.                                                                                                                                                                                                                          |  |  |  |

| 32  | IN8             | I/O                 | Ground/V <sub>BAT</sub> switch monitoring input with configurable current sink or source.                                                                                                                                                                                                                          |  |  |  |

| 33  | IN9             | I/O                 | Ground/V <sub>BAT</sub> switch monitoring input with configurable current sink or source.                                                                                                                                                                                                                          |  |  |  |

| 34  | IN10            | I/O                 | Ground switch monitoring input with current source                                                                                                                                                                                                                                                                 |  |  |  |

| 35  | IN11            | I/O                 | Ground switch monitoring input with current source                                                                                                                                                                                                                                                                 |  |  |  |

| 36  | IN12            | I/O                 | Ground switch monitoring input with current source                                                                                                                                                                                                                                                                 |  |  |  |

| 37  | Vs              | Р                   | Power supply input pin.                                                                                                                                                                                                                                                                                            |  |  |  |

| 38  | Vs              | Р                   | Power supply input pin.                                                                                                                                                                                                                                                                                            |  |  |  |

|     | EP              | Р                   | Exposed Pad. The exposed pad is not electrically connected to AGND or DGND. Connect EP to the board ground to achieve rated thermal and ESD performance.                                                                                                                                                           |  |  |  |

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted)<sup>(1)</sup>

|                      |                                                       | MIN  | MAX               | UNIT |

|----------------------|-------------------------------------------------------|------|-------------------|------|

|                      | V <sub>S</sub> , <del>INT</del>                       | -0.3 | 40 <sup>(2)</sup> | V    |

|                      | V <sub>DD</sub> , SCLK, SI, SO, <del>CS</del> , RESET | -0.3 | 6                 | V    |

| Input voltage        | IN0- IN23                                             | -24  | 40 <sup>(2)</sup> | V    |

| Input voltage        | CAP_Pre                                               | -0.3 | 5.5               | V    |

|                      | CAP_A                                                 | -0.3 | 5.5               | V    |

|                      | CAP_D                                                 | -0.3 | 2                 | V    |

| Operating junction t | temperature, T <sub>J</sub>                           | -40  | 150               | °C   |

| Storage temperatur   | re, T <sub>stg</sub>                                  | -55  | 155               | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

## 6.2 ESD Ratings

|                                                                                                                                                                                                                                      |                                          |                                                                                                                                                |                                    | VALUE                 | UNIT |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|-----------------------|------|

| <ul> <li>ESD generator parameters: storage capacitance = discharge resistance = 330 Ω or 2000 Ω</li> <li>Contact discharge, powered-up, per ISO- 10605:</li> <li>External components: capacitor = 15 nF; resistor = 330 Ω</li> </ul> |                                          | Human bady model (HPM), per AEC Q100 003(1)                                                                                                    | All pins                           | ±2000                 |      |

|                                                                                                                                                                                                                                      | Human-body model (HBM), per AEC Q100-002 | Pins IN0-IN23 <sup>(2)</sup>                                                                                                                   | ±4000                              |                       |      |

|                                                                                                                                                                                                                                      |                                          | All pins                                                                                                                                       | ±500                               |                       |      |

|                                                                                                                                                                                                                                      |                                          | Charged-device model (CDM), per AEC Q100-011                                                                                                   | Corner pins (pin 1, 19, 20 and 38) |                       |      |

| V <sub>(ESD)</sub>                                                                                                                                                                                                                   |                                          |                                                                                                                                                | Pins IN0-IN23                      | ±8000                 | V    |

|                                                                                                                                                                                                                                      |                                          | <ul> <li>External components: capacitor = 15 nF; resistor = 33 Ω</li> <li>ESD generator parameters: storage capacitance = 150 pF or</li> </ul> | Pins IN0-IN23                      | ±4000<br>±500<br>±750 |      |

<sup>(1)</sup> AEC Q100-002 indicates that HBM stressing shall be in accordance with the ANSI/ESDA/JEDEC JS-001 specification.

#### 6.3 Recommended Operating Conditions

over operating free-air temperature range and V<sub>S</sub> = 12 V (unless otherwise noted)

|                   |                                | MIN               | NOM MAX           | UNIT |

|-------------------|--------------------------------|-------------------|-------------------|------|

| V <sub>S</sub>    | Power supply voltage           | 4.5               | 35 <sup>(1)</sup> | V    |

| $V_{DD}$          | Logic supply voltage           | 3.0               | 5.5               | >    |

| V <sub>/INT</sub> | INT pin voltage                | 0                 | 35 <sup>(1)</sup> | V    |

| $V_{INX}$         | IN0 to IN23 input voltage      | 0                 | 35 <sup>(1)</sup> | V    |

| $V_{RESET}$       | RESET pin voltage              | 0                 | 5.5               | V    |

| $V_{SPI\_IO}$     | SPI input/output logic level   | 0                 | $V_{DD}$          | V    |

| f <sub>SPI</sub>  | SPI communication frequency    | 20 <sup>(2)</sup> | 4M                | Hz   |

| T <sub>A</sub>    | Operating free-air temperature | -40               | 125               | °C   |

<sup>(1)</sup> Tested for load dump and jump start conditions with nominal operating voltage no greater than 16 V for the life of a 12-V automotive system. Refer to Using TIC12400-Q1 in a 12 V Automotive System for more details.

<sup>(2)</sup> Tested for load dump and jump start conditions with nominal operating voltage no greater than 16V for the life of a 12-V automotive system. Refer to Using TIC12400-Q1 in a 12 V Automotive System for more details.

<sup>(2) ±4</sup>kV rating on pins IN0-IN23 are stressed with respect to GND (with AGND, DGND, and EP tied together).

<sup>(2)</sup> Lowest frequency characterized.

#### 6.4 Thermal Information

|                        |                                              | TIC12400-Q1 |      |

|------------------------|----------------------------------------------|-------------|------|

|                        | THERMAL METRIC <sup>(1)</sup>                | DCP (TSSOP) | UNIT |

|                        |                                              | 38 PINS     |      |

| $R_{\theta JA}$        | Junction-to-ambient thermal resistance       | 33.6        | °C/W |

| $R_{\theta JC(top)}$   | Junction-to-case (top) thermal resistance    | 18.4        | °C/W |

| $R_{\theta JB}$        | Junction-to-board thermal resistance         | 15.2        | °C/W |

| ΨЈТ                    | Junction-to-top characterization parameter   | 0.5         | °C/W |

| ΨЈВ                    | Junction-to-board characterization parameter | 15.0        | °C/W |

| R <sub>0</sub> JC(bot) | Junction-to-case (bottom) thermal resistance | 1.2         | °C/W |

<sup>(1)</sup> For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report.

# 6.5 Electrical Characteristics

over operating free-air temperature range,  $V_S = 4.5 \text{ V}$  to 35 V, and  $V_{DD} = 3 \text{ V}$  to 5.5 V (unless otherwise noted)

| PARAMETER                   |                                                                           | TEST CONDITIONS                                                                                                                                |                                                                                                                                       | MIN  | TYP | MAX | UNIT |

|-----------------------------|---------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|------|-----|-----|------|

| POWER SUPPLY                |                                                                           | •                                                                                                                                              |                                                                                                                                       |      |     |     |      |

| I <sub>S_CONT</sub>         | Continuous mode V <sub>S</sub> power supply current                       |                                                                                                                                                | ontinuous mode, I <sub>WETT</sub> = 10 mA, all switches open, no active DC conversion or comparator comparison, no unserviced terrupt |      | 5.6 | 7   | mA   |

| I <sub>S_POLL_COMP_25</sub> | Polling mode V <sub>S</sub>                                               | T <sub>A</sub> = 25°                                                                                                                           | Polling mode, t <sub>POLL</sub> = 64 ms, t <sub>POLL</sub> _ACT= 128                                                                  |      | 68  | 100 | μΑ   |

| I <sub>S_POLL_COMP_85</sub> | power supply average current in                                           | $T_A$ = -40° to 85°C                                                                                                                           | up all 24 shannels active and configured to                                                                                           |      | 68  | 110 | μΑ   |

| I <sub>S_POLL_COMP</sub>    | comparator mode                                                           | T <sub>A</sub> = -40° to 125°C                                                                                                                 | 10 mA, no unserviced interrupt                                                                                                        |      | 68  | 170 | μΑ   |

| I <sub>S_POLL_ADC_25</sub>  | Polling mode V <sub>S</sub>                                               | T <sub>A</sub> = 25°                                                                                                                           | Polling mode, t <sub>POLL</sub> = 64 ms, t <sub>POLL_ACT</sub> = 128                                                                  |      | 75  | 105 | μΑ   |

| I <sub>S_POLL_ADC_85</sub>  | power supply average current in                                           | $T_A$ = -40° to 85°C                                                                                                                           | µs, all 24 channels active and configured to ADC mode, all switches open, I <sub>WETT</sub> = 10 mA,                                  |      | 75  | 120 | μΑ   |

| I <sub>S_POLL_ADC</sub>     | ADC mode                                                                  | $T_A = -40^{\circ} \text{ to } 125^{\circ}\text{C}$                                                                                            | no unserviced interrupt                                                                                                               |      | 75  | 180 | μΑ   |

| I <sub>S_RESET</sub>        | Reset mode V <sub>S</sub> power supply current                            | Reset mode, V <sub>RESE</sub>                                                                                                                  | $V_{T} = V_{DD}$ . $V_{S} = 12$ V, all switches open, $T_{A} = 25$ °C                                                                 |      | 12  | 17  | μΑ   |

| I <sub>S_IDLE_25</sub>      |                                                                           | TRIGGER bit in CO unserviced interrup                                                                                                          | DNFIG register = logic 0, T <sub>A</sub> = 25°C, no t                                                                                 |      | 50  | 75  | μΑ   |

| I <sub>S_IDLE_85</sub>      | V <sub>S</sub> power supply average current in idle state                 | TRIGGER bit in CO unserviced interrup                                                                                                          | ONFIG register = logic 0, T <sub>A</sub> = -40°C to 85°C, no t                                                                        |      | 50  | 95  | μΑ   |

| I <sub>S_IDLE</sub>         | I laio state                                                              |                                                                                                                                                | TRIGGER bit in CONFIG register = logic 0, T <sub>A</sub> = -40°C to 125°C, no unserviced interrupt                                    |      |     | 145 | μΑ   |

| I <sub>DD</sub>             | Logic supply current from V <sub>DD</sub>                                 | SCLK = SI = 0 V, C                                                                                                                             | $\overline{CS} = \overline{INT} = V_{DD}$ , no SPI communication                                                                      |      | 1.5 | 10  | μΑ   |

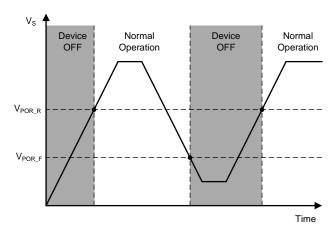

| V <sub>POR_R</sub>          | Power on reset                                                            |                                                                                                                                                | V <sub>S</sub> from device OFF condition resulting in $\overline{\text{INT}}$ flagged POR bit in the INT_STAT register                | 3.85 |     | 4.5 | V    |

| $V_{POR\_F}$                | (POR) voltage for V <sub>S</sub>                                          | Threshold for falling mode and loss of S                                                                                                       | g V <sub>S</sub> from device normal operation to reset PI communication                                                               | 1.95 |     | 2.8 | V    |

| $V_{OV\_R}$                 | Over-voltage (OV) condition for V <sub>S</sub>                            |                                                                                                                                                | V <sub>S</sub> from device normal operation resulting in nd a flagged OV bit in the INT_STAT register                                 | 35   |     | 40  | V    |

| V <sub>OV_HYST</sub>        | Over-voltage (OV) condition hysteresis for V <sub>S</sub>                 |                                                                                                                                                |                                                                                                                                       | 1    |     | 3.5 | V    |

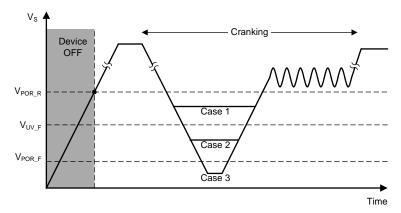

| $V_{UV\_R}$                 | Under-voltage (UV)                                                        |                                                                                                                                                | V <sub>S</sub> from under-voltage condition resulting in nd a flagged UV bit in the INT_STAT register                                 | 3.85 |     | 4.5 | V    |

| V <sub>UV_F</sub>           | condition for V <sub>S</sub>                                              | Threshold for falling V <sub>S</sub> from under-votlage condition resulting in INT pin assertion and a flagged UV bit in the INT_STAT register |                                                                                                                                       | 3.7  |     | 4.4 | V    |

| V <sub>UV_HYST</sub>        | Under-voltage (UV) condition hysteresis for V <sub>S</sub> <sup>(1)</sup> |                                                                                                                                                |                                                                                                                                       | 75   |     | 275 | mV   |

| $V_{DD_{\_F}}$              |                                                                           | Threshold for falling                                                                                                                          | g V <sub>DD</sub> resulting in loss of SPI communication                                                                              | 2.5  |     | 2.9 | V    |

| V <sub>DD_HYST</sub>        | Valid V <sub>DD</sub> voltage hysteresis                                  |                                                                                                                                                |                                                                                                                                       | 50   |     | 150 | mV   |

(1) Verified by design.

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

# **Electrical Characteristics (continued)**

over operating free-air temperature range,  $V_S = 4.5 \text{ V}$  to 35 V, and  $V_{DD} = 3 \text{ V}$  to 5.5 V (unless otherwise noted)

| PARAME                              | TER                                                                     |                                                                                                                    | TEST CONDITIONS                                                                                                          | MIN         | TYP     | MAX     | UNIT |

|-------------------------------------|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|-------------|---------|---------|------|

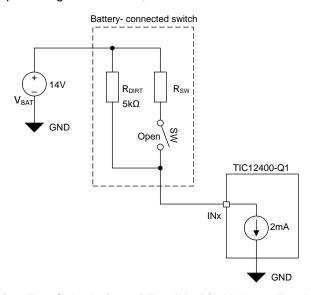

|                                     |                                                                         | WITCHES, MAXIMU                                                                                                    | JM RESISTANCE VALUE WITH SWITCH CLOS                                                                                     | ED ≤ 100Ω , | MINIMUM | RESISTA | NCE  |

| VALUE WITH SWITCH O                 | PEN 2 5000 (2)                                                          | 4 4 44:                                                                                                            |                                                                                                                          | 0.04        |         | 4.44    |      |

|                                     |                                                                         | 1 mA setting                                                                                                       | 4.5 V ≤ V <sub>S</sub> ≤ 35 V                                                                                            | 0.84        | 1       | 1.14    |      |

|                                     |                                                                         | 2 mA setting                                                                                                       | 457747                                                                                                                   | 1.71        | 2       | 2.32    |      |

| V                                   | Vetting current                                                         | 5 mA setting                                                                                                       | $4.5 \text{ V} \le \text{V}_{\text{S}} < 5 \text{ V}$                                                                    | 2.39        |         | 5.5     |      |

|                                     | accuracy for CSO                                                        |                                                                                                                    | 5 V ≤ V <sub>S</sub> ≤ 35 V                                                                                              | 4.3         | 5       | 5.6     | mA   |

| (:                                  | switch closed)                                                          | 10 mA setting                                                                                                      | 4.5 V ≤ V <sub>S</sub> < 6 V                                                                                             | 2.4         |         | 11      |      |

|                                     |                                                                         |                                                                                                                    | 6 V ≤ V <sub>S</sub> ≤ 35 V                                                                                              | 8.4         | 10      | 11.4    |      |

|                                     |                                                                         | 15 mA setting                                                                                                      | $4.5 \text{ V} \le \text{V}_{\text{S}} < 6.5 \text{ V}$                                                                  | 2.4         |         | 16.5    |      |

|                                     |                                                                         | 4 4 44:                                                                                                            | 6.5 V ≤ V <sub>S</sub> ≤ 35 V                                                                                            | 12.5        | 15      | 17      |      |

|                                     |                                                                         | 1 mA setting                                                                                                       | -                                                                                                                        | 0.75        | 1.1     | 2.05    |      |

| l <sub>v</sub>                      | Vetting current                                                         | 2 mA setting                                                                                                       | 4.5 V ≤ V <sub>S</sub> ≤ 35 V                                                                                            | 1.6         | 2.2     | 3.3     |      |

| I <sub>WETT</sub> (CSI)             | accuracy for CSI                                                        | 5 mA setting                                                                                                       | -                                                                                                                        | 4.3         | 5.6     | 7.1     | mA   |

| (:                                  | switch closed)                                                          | 10 mA setting                                                                                                      | 4577677                                                                                                                  | 9.2         | 11.5    | 13.4    |      |

|                                     |                                                                         | 15 mA setting                                                                                                      | $4.5 \text{ V} \le \text{V}_{\text{S}} < 6 \text{ V}$                                                                    | 11          | 16.5    | 19.2    |      |

|                                     |                                                                         | 10 m \ ac#in =                                                                                                     | 6 V ≤ V <sub>S</sub> ≤ 35V                                                                                               | 13.7        | 16.5    | 19.2    |      |

|                                     | /oltage drop from IN <sub>x</sub>                                       | 10 mA setting,<br>R <sub>SW</sub> = 5kΩ                                                                            |                                                                                                                          |             |         | 1.7     |      |

|                                     | oin to AGND across<br>CSI (switch open)                                 | 15 mA setting,                                                                                                     | $4.5 \text{ V} \le \text{V}_{\text{S}} \le 35 \text{V}$                                                                  |             |         | 4.7     | V    |

|                                     | Ser (emiter open)                                                       | $R_{SW}=5k\Omega$                                                                                                  |                                                                                                                          |             |         | 1.7     |      |

|                                     | Voltage drop from<br>INx pin to ground<br>across CSI (switch<br>closed) | 2mA setting, $I_{IN}$ =<br>1mA (4.5V $\leq$ VS $\leq$ 35V)                                                         | ≤ = = = = = = = = = = = = = = = = = = =                                                                                  |             |         | 1.2     | V    |

|                                     |                                                                         | 5mA setting, I <sub>IN</sub> =<br>1mA or 2mA                                                                       |                                                                                                                          |             |         | 1.3     | V    |

| VCSI_DROP_CLOSED a                  |                                                                         | 10mA setting, I <sub>IN</sub> =<br>1mA, 2mA, or<br>5mA                                                             |                                                                                                                          |             |         | 1.5     | V    |

|                                     |                                                                         | 15mA setting, I <sub>IN</sub> =<br>1mA, 2mA, 5mA,<br>or 10mA                                                       |                                                                                                                          |             |         | 2.1     | V    |

| WETTING CURRENT AC                  | CURACY (ANALOG S                                                        | SWITCHES)                                                                                                          |                                                                                                                          |             |         |         |      |

|                                     | •                                                                       | 1 mA setting                                                                                                       | 0.88                                                                                                                     |             | 1       | 1.13    |      |

|                                     |                                                                         | 2 mA setting                                                                                                       | $4.5 \text{ V} \le \text{V}_{\text{S}} \le 35 \text{ V}, \text{ V}_{\text{S}} - \text{V}_{\text{INX}} \ge 2.5 \text{ V}$ | 1.8         | 2       | 2.25    | -    |

| l <sub>v</sub>                      | Netting current                                                         |                                                                                                                    | $5.5 \text{ V} \le \text{V}_{\text{S}} \le 35 \text{ V}, \text{V}_{\text{S}} - \text{V}_{\text{INX}} \ge 2.5 \text{ V}$  | 4.3         | 5       | 5.5     |      |

|                                     | accuracy                                                                | 5 mA setting                                                                                                       | 5.5 V ≤ V <sub>S</sub> ≤ 35 V, V <sub>S</sub> − V <sub>INX</sub> ≥ 3 V                                                   | 4.5         | 5       | 5.5     | mA   |

|                                     |                                                                         | 10 mA setting                                                                                                      | 6 V ≤ V <sub>S</sub> ≤ 35 V, V <sub>S</sub> − V <sub>INX</sub> ≥ 4 V                                                     | 9           | 10      | 11      |      |

|                                     |                                                                         | 15 mA setting                                                                                                      | $6.5 \text{ V} \le \text{V}_{\text{S}} \le 35 \text{ V}, \text{ V}_{\text{S}} - \text{V}_{\text{INX}} \ge 5 \text{ V}$   | 12.5        | 15      | 16.5    |      |

| LEAKAGE CURRENTS                    |                                                                         |                                                                                                                    |                                                                                                                          |             |         | +       |      |

| I <sub>IN LEAK OFF</sub>            | _eakage current at                                                      | $0 \text{ V} \leq \text{V}_{\text{INx}} \leq \text{V}_{\text{S}}$ , ch                                             | nannel disabled (EN_INx register bit= logic 0)                                                                           | -4          |         | 5.3     |      |

| . ir                                | nput INx when<br>channel is disabled                                    | $0 \text{ V} \le \text{V}_{\text{INx}} \le \text{V}_{\text{S}}$ , ch<br>$\text{T}_{\text{A}} = 25^{\circ}\text{C}$ | nannel disabled (EN_INx register bit= logic 0),                                                                          | -0.5        |         | 0.5     | μΑ   |

| L                                   | _eakage current at                                                      |                                                                                                                    |                                                                                                                          |             |         |         | μA   |

| IN_LEAK_0mA v                       | nput INx when<br>vetting current<br>setting is 0mA                      | $0 \ V \le V_{INx} \le 6 \ V,  6$                                                                                  | $V \le V_S \le 35 \text{ V}$ , $I_{WETT}$ setting = 0 mA                                                                 | -110        |         | 110     | μΑ   |

| I <sub>IN_LEAK_LOSS_OF_GND</sub> ii | Leakage current at<br>nput INx under loss<br>of GND condition           | $V_S = 24 \text{ V}, 0 \text{ V} \le V_I$<br>= 24 V, $V_{DD}$ shorter                                              | <sub>Nx</sub> ≤ 24 V, all grounds (AGND, DGND, and EP) d to the grounds <sup>(1)</sup>                                   | -5          |         |         | μA   |

| I <sub>IN_LEAK_LOSS_OF_VS</sub> ii  | Leakage current at nput INx under loss of V <sub>S</sub> condition      | 0 V ≤ V <sub>INx</sub> ≤ 24 V, V                                                                                   | $V_S$ shorted to the grounds = 0 V, $V_{DD}$ = 0 V                                                                       |             |         | 5       | μA   |

| LOGIC LEVELS                        |                                                                         |                                                                                                                    |                                                                                                                          |             |         |         |      |

| V                                   | NT output low                                                           | $I_{/INT} = 2 \text{ mA}$                                                                                          |                                                                                                                          |             |         | 0.35    | V    |

| V <sub>/INT_L</sub>                 | voltage .                                                               | I <sub>/INT</sub> = 4 mA                                                                                           |                                                                                                                          |             |         | 0.6     | V    |

Copyright © 2017, Texas Instruments Incorporated

# **Electrical Characteristics (continued)**

over operating free-air temperature range,  $V_S = 4.5 \text{ V}$  to 35 V, and  $V_{DD} = 3 \text{ V}$  to 5.5 V (unless otherwise noted)

| Р                     | ARAMETER                                    |                                                                                                                                                   | TEST CONDITIONS                                                                              | MIN                | TYP  | MAX                | UNIT |

|-----------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|--------------------|------|--------------------|------|

| $V_{SO\_L}$           | SO output low voltage                       | I <sub>SO</sub> = 2 mA                                                                                                                            |                                                                                              |                    |      | $0.2V_{DD}$        | V    |

| V <sub>SO_H</sub>     | SO output high voltage                      | I <sub>SO</sub> = -2 mA                                                                                                                           |                                                                                              | 0.8V <sub>DD</sub> |      |                    | V    |

| V <sub>IN_L</sub>     | SI, SCLK, and CS input low voltage          |                                                                                                                                                   |                                                                                              |                    |      | 0.3V <sub>DD</sub> | V    |

| V <sub>IN_H</sub>     | SI, SCLK, and CS input high voltage         |                                                                                                                                                   |                                                                                              | 0.7V <sub>DD</sub> |      |                    | V    |

| V <sub>RESET_L</sub>  | RESET input low voltage                     |                                                                                                                                                   |                                                                                              |                    |      | 0.8                | V    |

| V <sub>RESET_H</sub>  | RESET input high voltage                    |                                                                                                                                                   |                                                                                              |                    |      |                    | V    |

| R <sub>RESET_25</sub> | RESET pin internal                          | V <sub>RESET</sub> = 0 to 5.5                                                                                                                     | <sub>SET</sub> = 0 to 5.5V, T <sub>A</sub> =25°C                                             |                    | 1.25 | 1.7                | MO   |

| R <sub>RESET</sub>    | pull-down resistor                          | V <sub>RESET</sub> = 0 to 5.5                                                                                                                     | <sub>ESET</sub> = 0 to 5.5V, T <sub>A</sub> = -40° to 125°C                                  |                    |      | 2.1                | ΜΩ   |

| SWITCH INPUT A        | AND V <sub>S</sub> MEASUREMENT CO           | NVERSION PARA                                                                                                                                     | METERS                                                                                       |                    |      |                    |      |

| RES                   | Resolution                                  |                                                                                                                                                   |                                                                                              | 10                 |      |                    | Bits |

|                       |                                             |                                                                                                                                                   | 4.5 V $\leq$ V <sub>S</sub> $\leq$ 35 V, 100 $\Omega$ resistance to ground at INx            | 12                 | 17   | 26                 |      |

|                       |                                             | 1mA setting                                                                                                                                       | 4.5 V $\leq$ V_S $\leq$ 35 V, 300 $\Omega$ resistance to ground at INx                       | 42                 | 51   | 64                 | LSB  |

|                       |                                             |                                                                                                                                                   | 4.5 V $\leq$ V $_{S} \leq$ 35 V, 600 $\Omega$ resistance to ground at INx                    | 87                 | 102  | 122                |      |

|                       |                                             |                                                                                                                                                   | 4.5 V $\leq$ V <sub>S</sub> $\leq$ 35 V, 100 Ω resistance to ground at INx                   | 28                 | 34   | 45                 | LSB  |

|                       |                                             | 2mA setting                                                                                                                                       | $4.5 \text{ V} \le \text{V}_{\text{S}} \le 35 \text{ V}$ , 300 Ω resistance to ground at INx | 89                 | 102  | 122                |      |

|                       |                                             |                                                                                                                                                   | $4.5 \text{ V} \le \text{V}_{\text{S}} \le 35 \text{ V}$ , 600 Ω resistance to ground at INx | 181                | 205  | 236                |      |

|                       |                                             | 5mA setting                                                                                                                                       | 5 V ≤ V <sub>S</sub> ≤ 35 V, 100 $\Omega$ resistance to ground at INx                        | 72                 | 85   | 105                | LSB  |

| OUT <sub>SW</sub>     | Switch input conversion output              |                                                                                                                                                   | 5 V $\leq$ V <sub>S</sub> $\leq$ 35 V, 300 $\Omega$ resistance to ground at INx              | 223                | 256  | 296                |      |

|                       |                                             |                                                                                                                                                   | 5 V $\leq$ V <sub>S</sub> $\leq$ 35 V, 600 $\Omega$ resistance to ground at INx              | 393                | 512  | 620                |      |

|                       |                                             | 10mA setting                                                                                                                                      | 6 V ≤ V <sub>S</sub> ≤ 35 V, 100 $\Omega$ resistance to ground at INx                        | 142                | 171  | 202                |      |

|                       |                                             |                                                                                                                                                   | 6 V ≤ V <sub>S</sub> ≤ 35 V, 250 $\Omega$ resistance to ground at INx                        | 333                | 427  | 486                |      |

|                       |                                             |                                                                                                                                                   | 6 V $\leq$ V $_{S}$ $\leq$ 35 V, 400 $\Omega$ resistance to ground at INx                    | 430                | 683  | 823                |      |

|                       |                                             |                                                                                                                                                   | 6.5 V $\leq$ V <sub>S</sub> $\leq$ 35 V, 100 Ω resistance to ground at INx                   | 166                | 256  | 301                |      |

|                       |                                             | 15mA setting                                                                                                                                      | 6.5 V $\leq$ Vs $\leq$ 35 V, 200 $\Omega$ resistance to ground at INx                        | 325                | 512  | 582                | LSB  |

|                       |                                             |                                                                                                                                                   | 6.5 V $\leq$ V <sub>S</sub> $\leq$ 35 V, 300 $\Omega$ resistance to ground at INx            | 450                | 768  | 879                |      |

| OUT                   | V <sub>S</sub> measurement                  | V <sub>S</sub> measurement                                                                                                                        | ts (V <sub>S</sub> ≥ 4.5V), VS_RATIO= 0 in register CONFIG                                   |                    |      | ±2%                |      |

| OUT <sub>VS</sub>     | output tolerance to full-scale range        | V <sub>S</sub> measurement                                                                                                                        | ts (V <sub>S</sub> ≥ 4.5V), VS_RATIO= 1 in register CONFIG                                   |                    |      | ±2%                |      |

|                       |                                             | INx measuremer                                                                                                                                    | nts                                                                                          |                    | 6    |                    |      |

| $V_{FSR}$             | Input full-scale range                      | $V_S$ measurements ( $V_S \ge 4.5V$ ), $VS_RATIO = 0$ in register CONFIG $V_S$ measurements ( $V_S \ge 4.5V$ ), $VS_RATIO = 1$ in register CONFIG |                                                                                              |                    | 9    |                    | V    |

|                       |                                             |                                                                                                                                                   |                                                                                              |                    | 30   |                    |      |

| R <sub>IN, SC</sub>   | Input resistance                            | INx measuremen                                                                                                                                    | nts                                                                                          |                    | 240  |                    | kΩ   |

|                       |                                             | INx measuremen                                                                                                                                    | nts                                                                                          |                    | 2    |                    |      |

| R <sub>RATIO</sub>    | Input voltage divider factor <sup>(1)</sup> | V <sub>S</sub> measurement                                                                                                                        | ts ( $V_S \ge 4.5 \text{ V}$ ), $VS\_RATIO = 0$ in register                                  |                    | 3    |                    | -    |

|                       |                                             | V <sub>S</sub> measurements (V <sub>S</sub> ≥ 4.5 V), VS_RATIO = 1 in register CONFIG                                                             |                                                                                              |                    | 10   |                    | -    |

Submit Documentation Feedback

Copyright © 2017, Texas Instruments Incorporated

# **Electrical Characteristics (continued)**

over operating free-air temperature range,  $V_S = 4.5 \text{ V}$  to 35 V, and  $V_{DD} = 3 \text{ V}$  to 5.5 V (unless otherwise noted)

| PAI                              | RAMETER                          | TEST CONDITIONS    | MIN  | TYP MAX | UNIT     |

|----------------------------------|----------------------------------|--------------------|------|---------|----------|

| COMPARATOR PA                    | RAMETERS                         |                    |      |         | <u> </u> |

| V <sub>TH_ COMP_2V</sub>         | Comparator threshold for 2 V     | THRES_COMP = 2 V   | 1.85 | 2.25    | 5 V      |

| V <sub>TH_ COMP_2p7V</sub>       | Comparator threshold for 2.7 V   | THRES_COMP = 2.7 V | 2.4  | 2.9     | V        |

| V <sub>TH_ COMP_3V</sub>         | Comparator threshold for 3 V     | THRES_COMP = 3 V   | 2.85 | 3.0     | 3 V      |

| V <sub>TH_ COMP_4V</sub>         | Comparator threshold for 4 V     | THRES_COMP = 4 V   | 3.7  | 4.35    | 5 V      |

|                                  |                                  | THRES_COMP = 2 V   | 4.5  |         |          |

| M                                | Minimum V <sub>S</sub>           | THRES_COMP = 2.7 V | 5    |         | V        |

| V <sub>S_COMP</sub>              | requirement for proper detection | THRES_COMP = 3 V   | 5.5  |         | V        |

|                                  |                                  | THRES_COMP = 4 V   | 6.5  |         |          |

| R <sub>IN, COMP</sub> equivalent |                                  | THRES_COMP = 2 V   | 30   | 130     |          |

|                                  | Comparator                       | THRES_COMP = 2.7 V | 35   | 130     | 1.0      |

|                                  | equivalent input<br>resistance   | THRES_COMP = 3 V   | 35   | 105     | kΩ       |

|                                  |                                  | THRES_COMP = 4 V   | 43   | 95      |          |

Copyright © 2017, Texas Instruments Incorporated

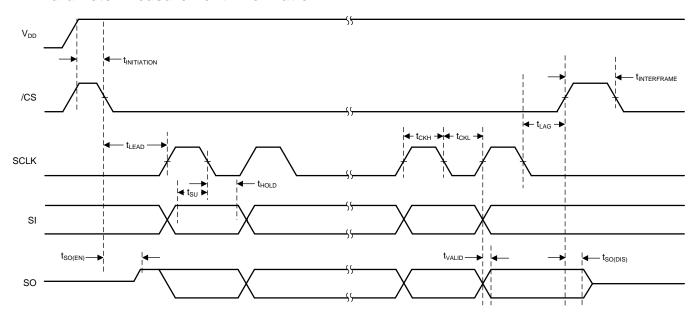

# 6.6 Timing Requirements

$V_S$ = 4.5 V to 35 V,  $V_{DD}$ = 3 V to 5.5 V, and 10 pF capacitive load on SO unless otherwise noted; verified by design and characterization

|                              | PARAMETER                                                                                            | TEST CONDITION                                 | MIN  | NOM | MAX | UNIT |

|------------------------------|------------------------------------------------------------------------------------------------------|------------------------------------------------|------|-----|-----|------|

| SWITCH N                     | MONITORING, INTERRUPT, STARTUP AND RESET                                                             |                                                | "    |     |     |      |

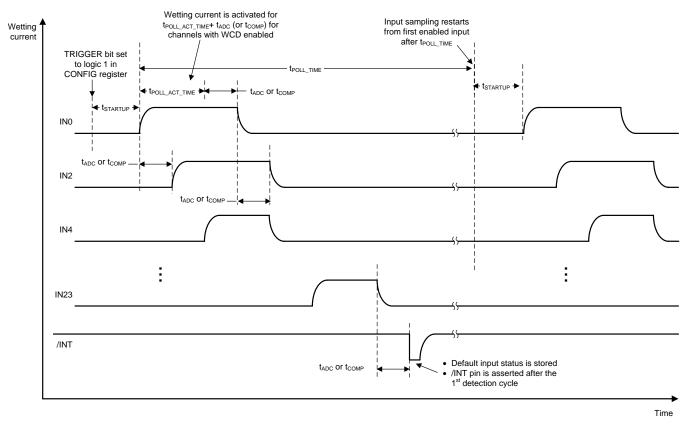

| t <sub>POLL_ACT</sub>        | Polling active time accuracy                                                                         | Polling mode                                   | -12% |     | 12% |      |

| t <sub>POLL_ACT</sub>        | Polling active time accuracy for matrix inputs                                                       | Polling mode with matrix enabled               | -12% |     | 12% |      |

| t <sub>POLL</sub>            | Polling time accuracy                                                                                | Polling mode                                   | -12% |     | 12% |      |

| $t_{\text{COMP}}$            | Comparator detection time                                                                            |                                                |      | 18  |     | μs   |

| t <sub>ADC</sub>             | ADC Conversion time                                                                                  | Sample and hold time included                  |      | 24  |     | μs   |

| t <sub>CCP_TRAN</sub>        | Transition time between last input sampling and start of clean current                               |                                                |      | 20  |     | μs   |

| t <sub>CCP_ACT</sub>         | Clean current active time                                                                            |                                                | -12% |     | 12% |      |

| t <sub>STARTUP</sub>         | Polling startup time                                                                                 |                                                | 200  | 300 | 400 | μs   |

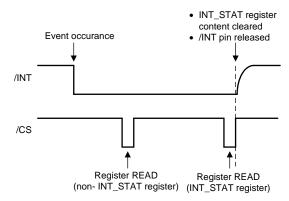

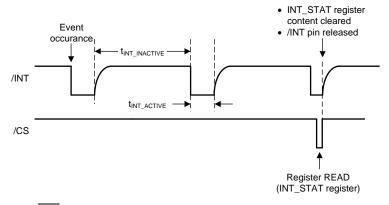

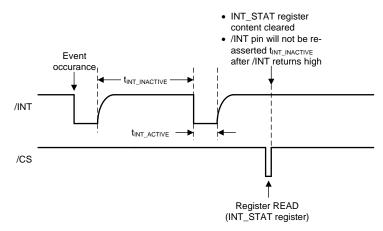

| t <sub>INT_ACTIV</sub>       | Active INT assertion duration                                                                        |                                                | 1.5  | 2   | 2.5 | ms   |

| t <sub>INT_INACT</sub>       | INT de-assertion duration during a pending interrupt                                                 |                                                | 3    | 4   | 5   | ms   |

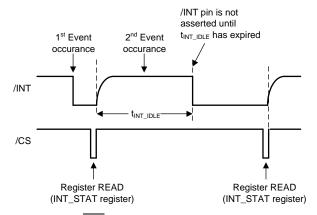

| t <sub>INT_IDLE</sub>        | Interrupt idle time                                                                                  |                                                | 80   | 100 | 120 | μs   |

| t <sub>RESET</sub>           | Time required to keep the RESET pin high to successfully reset the device (no pending interrupt) (1) |                                                | 2    |     |     | μs   |

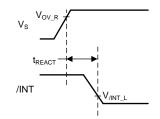

| t <sub>REACT</sub>           | Delay between a fault event (OV, UV, TW, or TSD) to a high to low transition on the INT pin          | See Figure 13 for OV example.                  |      |     | 20  | μs   |

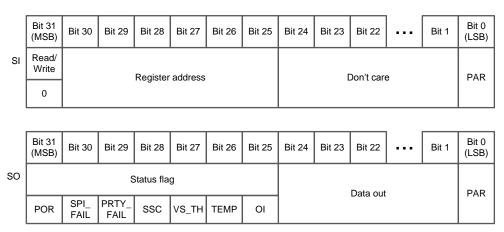

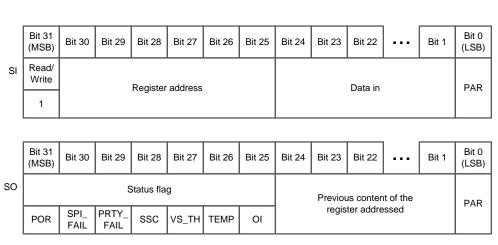

| SPI INTER                    | RFACE                                                                                                |                                                |      |     |     |      |

| t <sub>LEAD</sub>            | Falling edge of CS to rising edge of SCLK setup time                                                 |                                                | 100  |     |     | ns   |

| t <sub>LAG</sub>             | Falling edge of SCLK to rising edge of CS setup time                                                 |                                                | 100  |     |     | ns   |

| t <sub>SU</sub>              | SI to SCLK falling edge setup time                                                                   |                                                | 30   |     |     | ns   |

| t <sub>HOLD</sub>            | SI hold time after falling edge of SCLK                                                              |                                                | 20   |     |     | ns   |

| $t_{VALID}$                  | Time from rising edge of SCLK to valid SO data                                                       |                                                |      |     | 70  | ns   |

| t <sub>SO(EN)</sub>          | Time from falling edge of $\overline{\text{CS}}$ to SO low-impedance                                 |                                                |      |     | 60  | ns   |

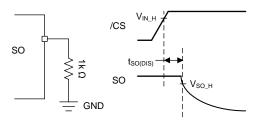

| t <sub>SO(DIS)</sub>         | Time from rising edge of CS to SO high-impedance                                                     | Loading of 1 k $\Omega$ to GND. See Figure 14. |      |     | 60  | ns   |

| t <sub>R</sub>               | SI, CS, and SCLK signals rise time                                                                   |                                                |      | 5   | 30  | ns   |

| t <sub>F</sub>               | SI, $\overline{\text{CS}}$ , and SCLK signals fall time                                              |                                                |      | 5   | 30  | ns   |

| t <sub>INTER_FR</sub><br>AME | Delay between two SPI communication (CS low) sequences                                               |                                                | 1.5  |     |     | μs   |

| t <sub>CKH</sub>             | SCLK High time                                                                                       |                                                | 120  |     |     | ns   |

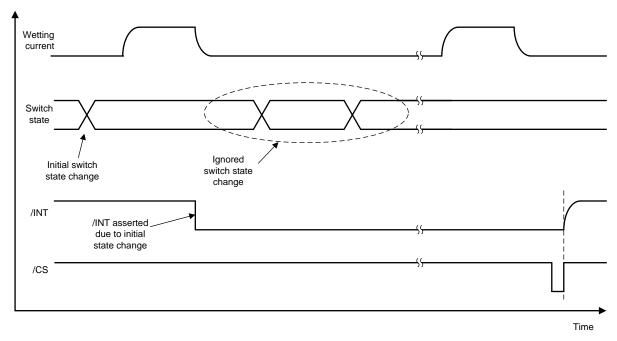

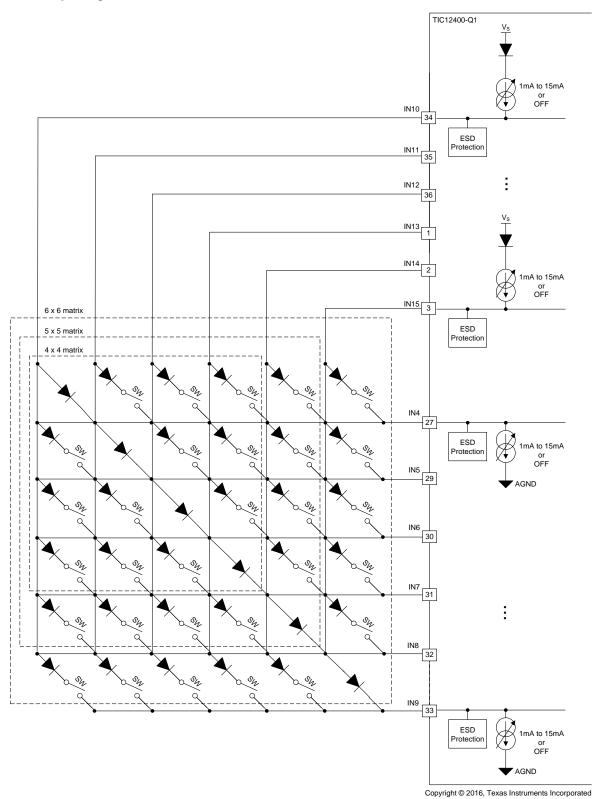

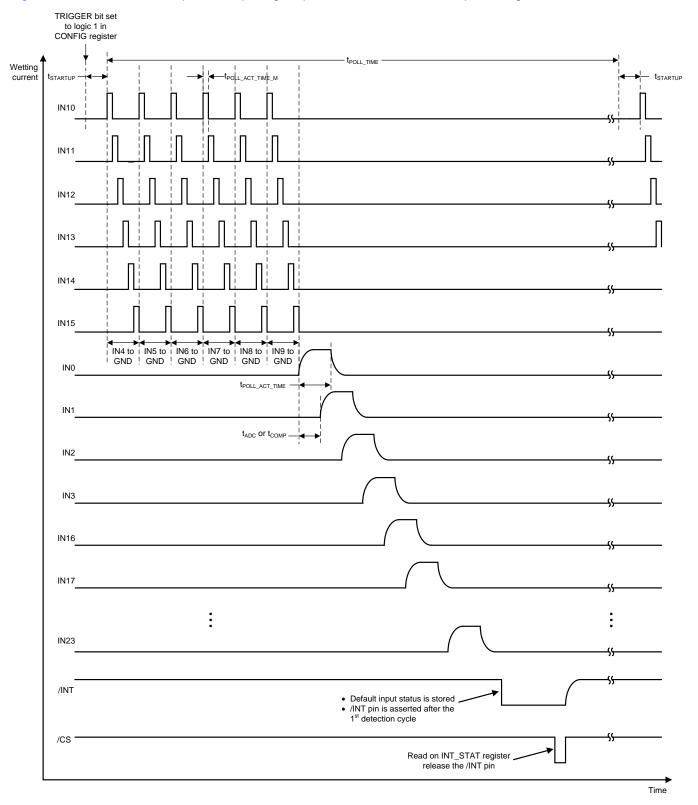

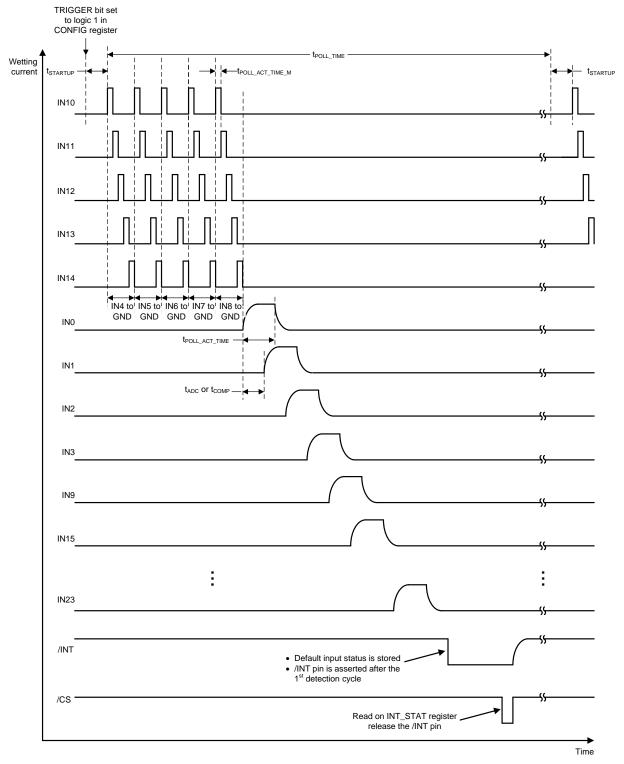

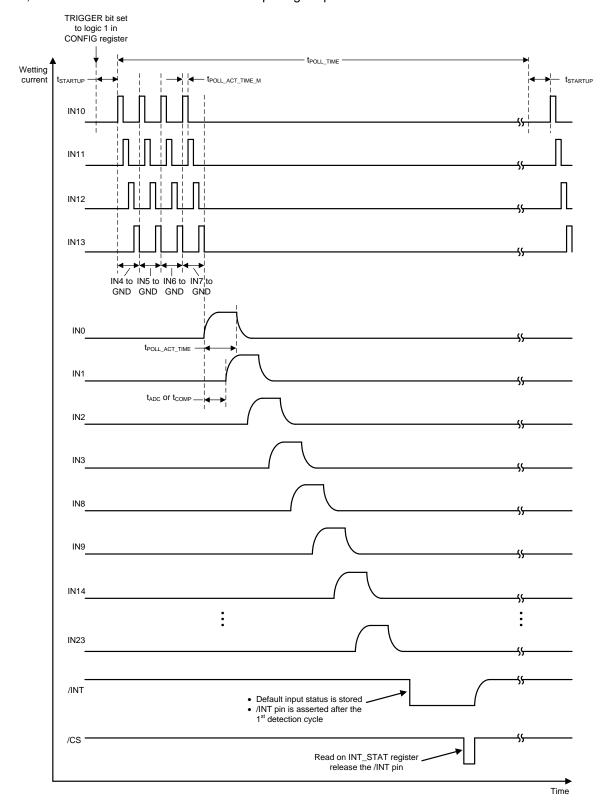

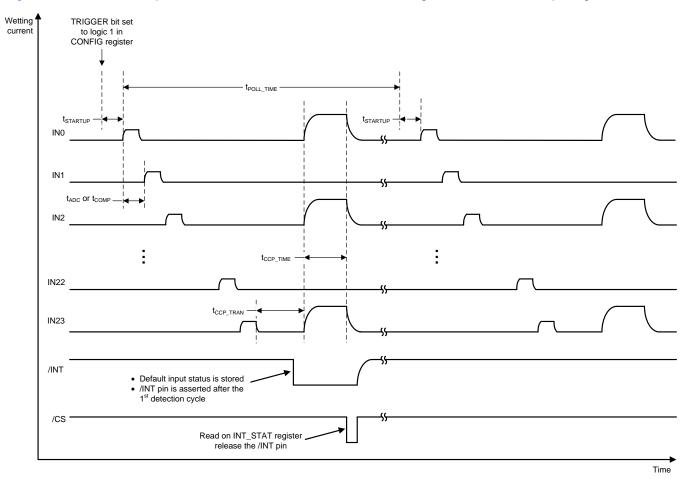

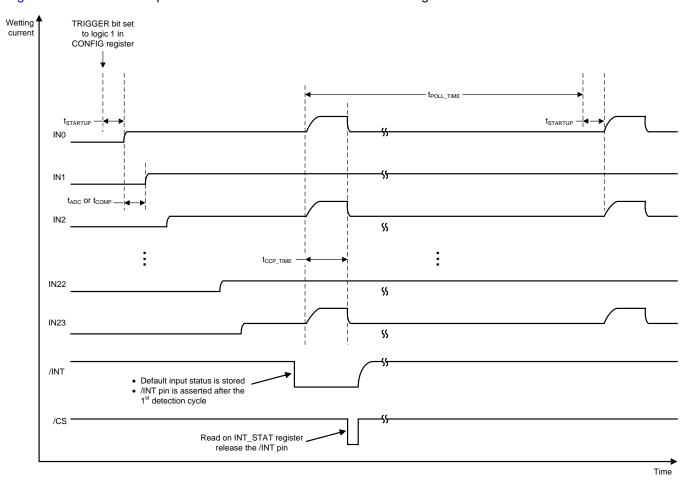

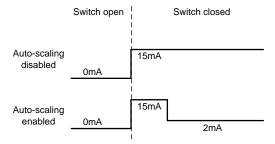

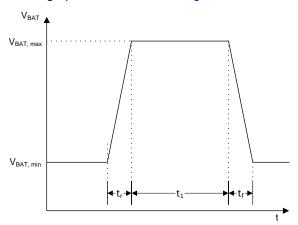

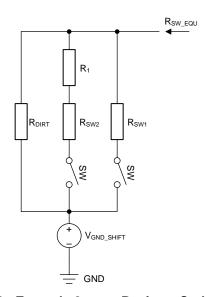

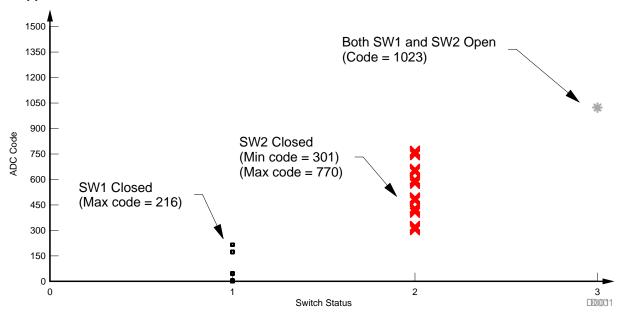

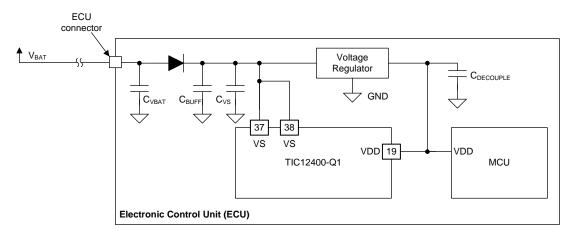

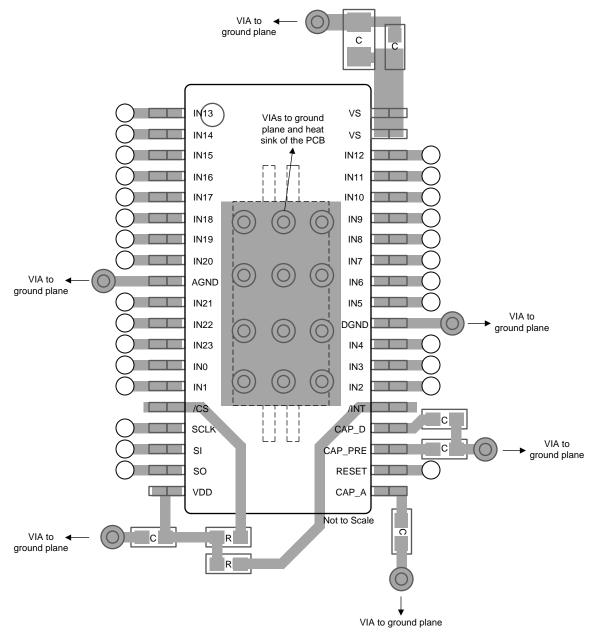

| t <sub>CKL</sub>             | SCLK Low time                                                                                        |                                                | 120  |     |     | ns   |